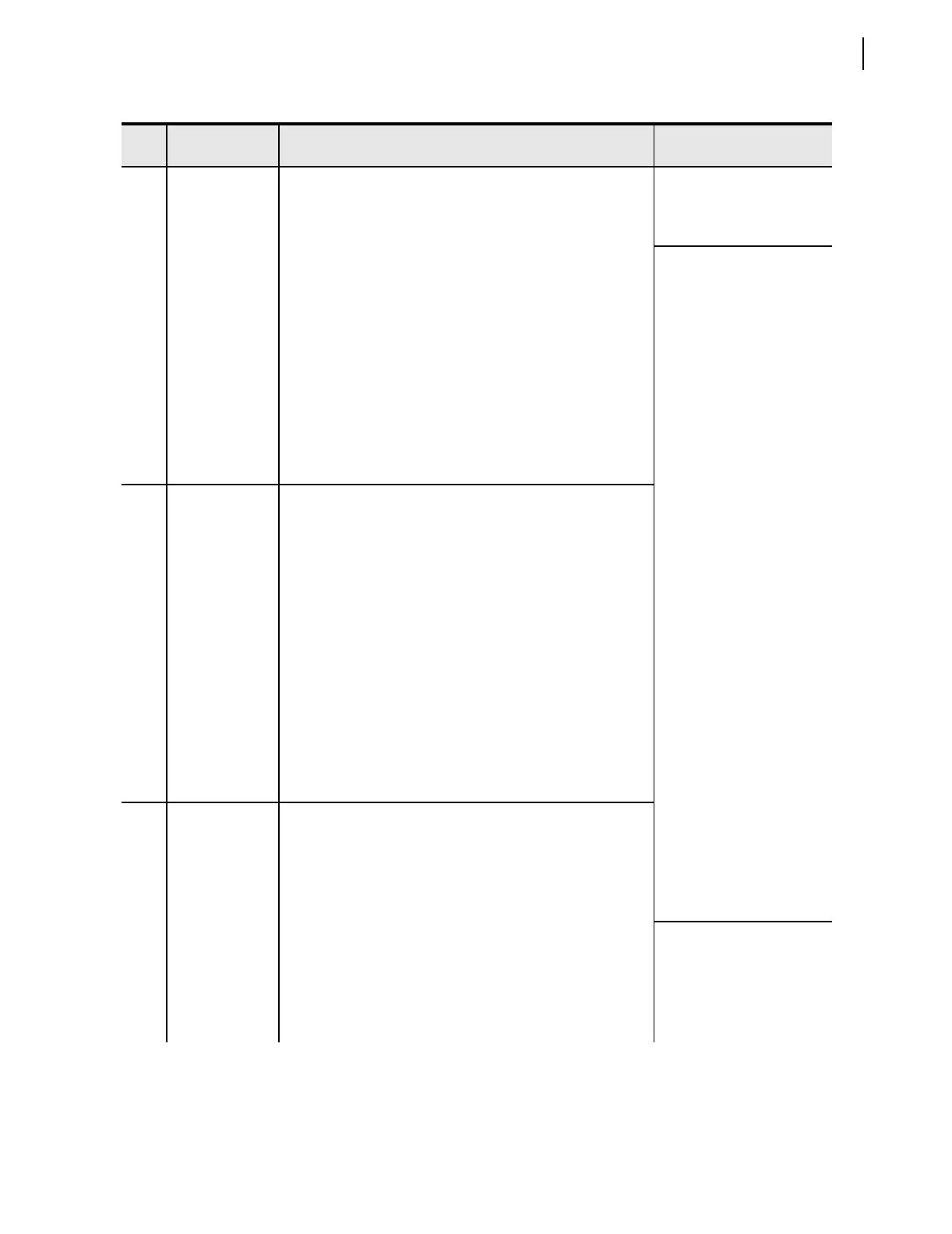

4.15

Date Code 20110408 Instruction Manual SEL-551 Relay

Setting the Relay

Relay Word Bit Setting Reference Information

2 51Q1

a

Negative-sequence current above pickup setting 51Q1P for negative-

sequence time-overcurrent element 51Q1T (see Figure 3.12)

Event report triggering,

Testing

51Q2

a

Negative-sequence current above pickup setting 51Q2P for negative-

sequence time-overcurrent element 51Q2T (see Figure 3.12)

51Q1T

a

First negative-sequence time-overcurrent element timed out

(see Figure 3.12)

Tripping

51Q2T

a

Second negative-sequence time-overcurrent element timed out

(see Figure 3.12)

50P1 First phase instantaneous overcurrent element picked up

(see Figure 3.4)

50P2 Second phase instantaneous overcurrent element picked up

(see Figure 3.4)

50P3 Third phase instantaneous overcurrent element picked up

(see Figure 3.4)

50P4 Fourth phase instantaneous overcurrent element picked up

(see Figure 3.4)

3 50P5 Fifth phase instantaneous overcurrent element picked up

(see Figure 3.4)

50P6 Sixth phase instantaneous overcurrent element picked up

(see Figure 3.4)

50N1 First neutral ground instantaneous overcurrent element picked up

(see Figure 3.6)

50N2 Second neutral ground instantaneous overcurrent element picked up

(see Figure 3.6)

50G1 First residual ground instantaneous overcurrent element picked up

(see Figure 3.7)

50G2 Second residual ground instantaneous overcurrent element picked up

(see Figure 3.7)

50Q1

a

First negative-sequence instantaneous overcurrent element picked up

(see Figure 3.8)

50Q2

a

Second negative-sequence instantaneous overcurrent element picked

up (see Figure 3.8)

4 50A Single-phase instantaneous overcurrent element picked up

(channel IA; see Figure 3.5)

50B Single-phase instantaneous overcurrent element picked up

(channel IB; see Figure 3.5)

50C Single-phase instantaneous overcurrent element picked up

(channel IC; see Figure 3.5)

IN1 Optoisolated input IN1 asserted (see Figure 3.1) Circuit breaker status, etc.

IN2 Optoisolated input IN2 asserted (see Figure 3.1)

OC

b

Asserts 1/8 cycle for Open Command execution (see Figure 3.13)

CC

b

Asserts 1/8 cycle for Close Command execution (see Figure 3.14)

CF Close Failure logic output asserted (see Figure 3.14) Indication

Ta b le 4 . 6 Re la y W o rd B i t D e f i n i t io n s (Sheet 2 of 4)

Row Bit Definition

Primary

Application

Loading...

Loading...