Sun Microelectronics

94

UltraSPARC User’s Manual

2. If UltraSPARC receives the S_REQ for the dirty cache block in the

Writeback Buffer after the S_WAB/S_WBCAN reply for the Writeback

transaction and before the S_RBU/S_RBS reply for the read transaction, the

S_REQ completes atomically and can either result in P_SACK or

P_SNACK. Both P_REPLYs are correct, since the former ends up sourcing

the same data that was just written to memory.

If an S_REQ receives a P_SNACK, SC can send an S_CRAB, but UltraSPARC re-

turns undefined data. There is no reason for SC to send an S_CRAB in this case.

7.6 Cache Coherence Protocol

This section describes the protocol used to maintain coherency between an

UltraSPARC’s internal caches, the E-Cache, and the system. “System” refers to

any other location within the same coherency domain as UltraSPARC; for exam-

ple, it includes caches of other processors connected to the interconnect. The

cache coherence protocol operates on Physically Indexed, Physically Tagged

(PIPT) writeback caches.

The E-Cache maintains inclusion for both the I-Cache and the D-Cache; that is, all

lines in the internal caches are also in the E-Cache. The system is responsible only

for maintaining E-Cache coherency; UltraSPARC ensures that the internal caches

are coherent.

The cache coherence protocol is point-to-point write-invalidate; that is, SC must

issue separate S_INV requests to each cache containing a copy of the line it needs

to invalidate. There are no “broadcast” transmissions on the interconnect.

The protocol is based on the MOESI states maintained in the E-Cache tags of each

master port. Note that subsets of the states, such as MSI, or MOSI, could be used.

Bits within each E-Cache tag define the cache line state of each line:

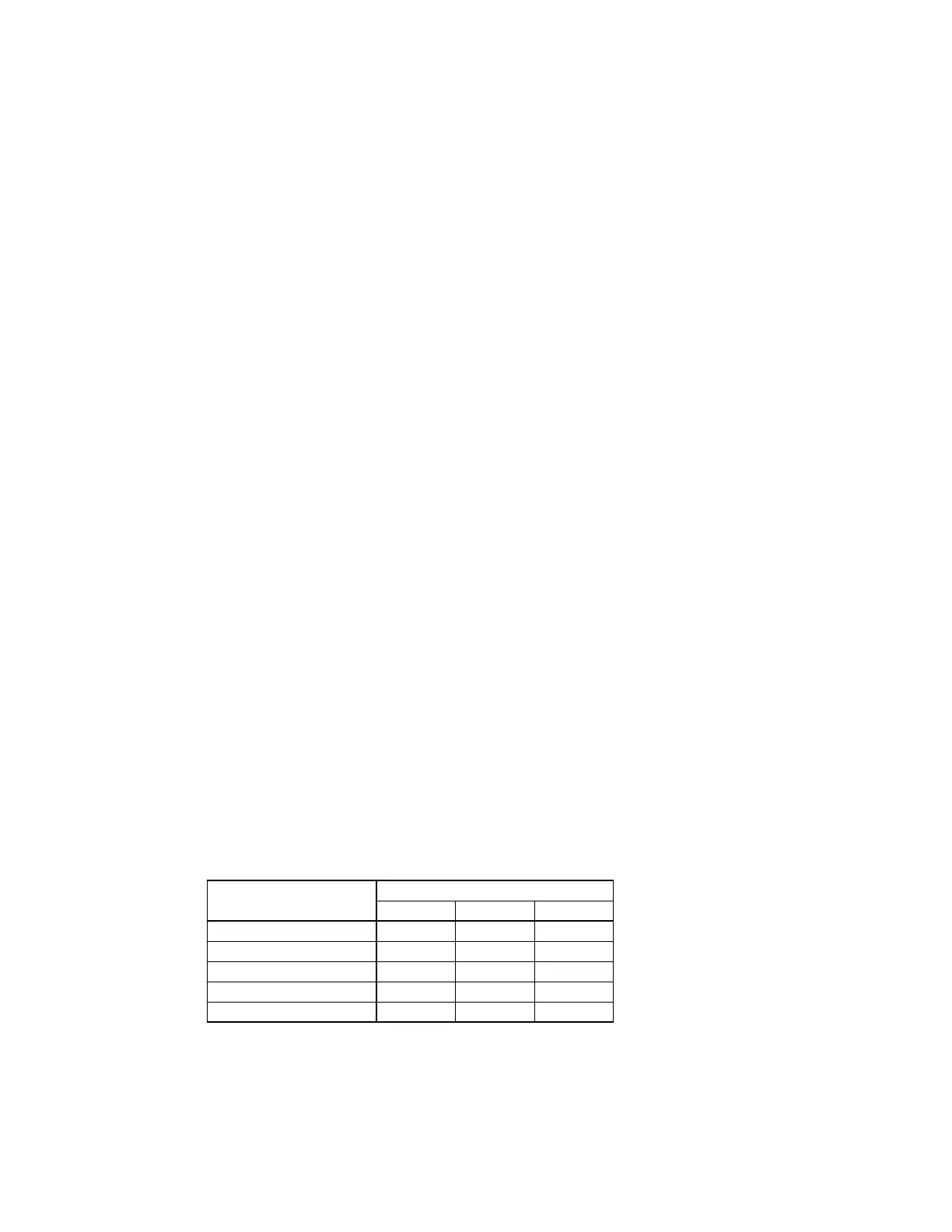

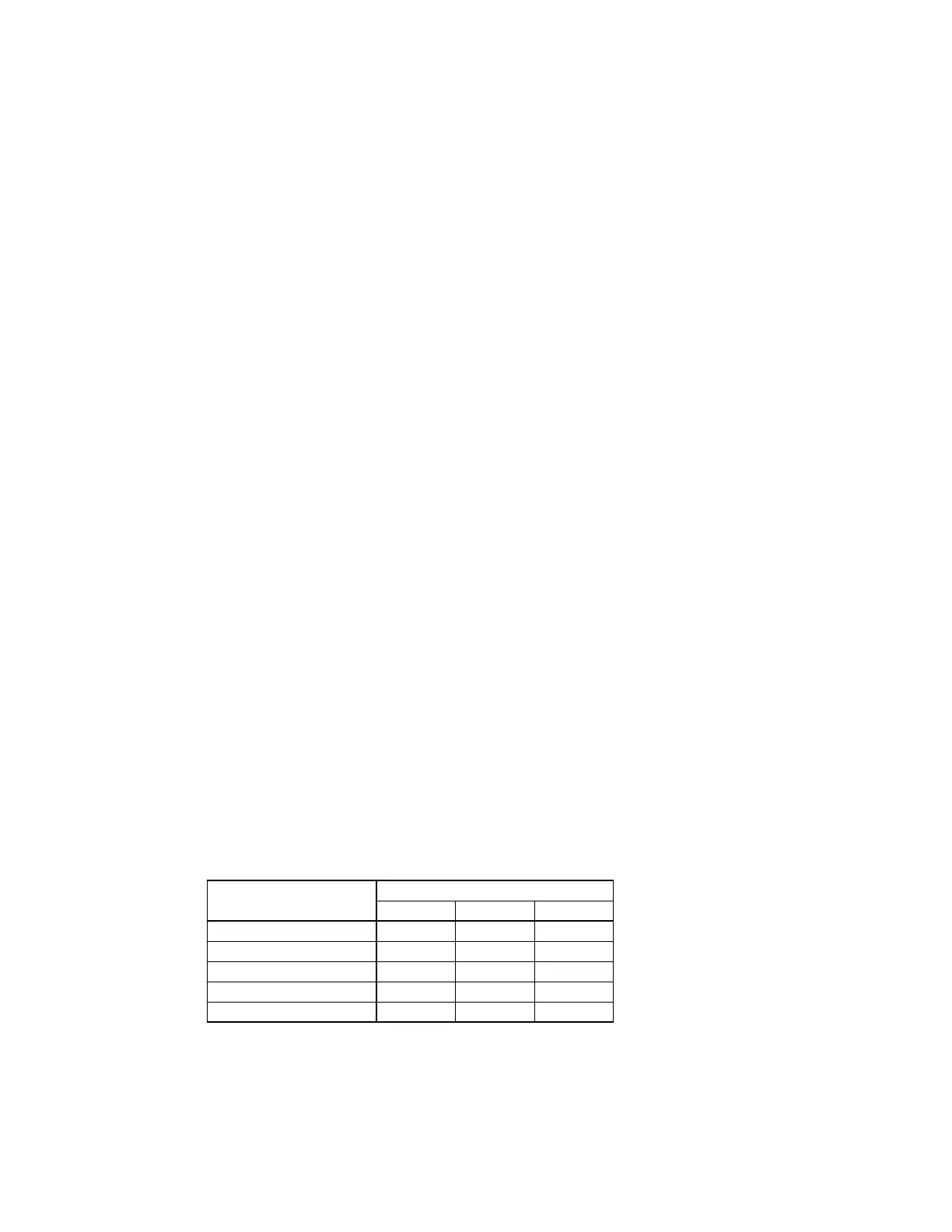

Table 7-7 E-Cache Coherency State Definition

State Bit

Line State Valid Modified Exclusive

Invalid (I) 0 X X

Shared Clean (S) 1 0 0

Exclusive Clean (E) 1 0 1

Shared Modified (O) 1 1 0

Exclusive Modified (M) 1 1 1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...