Sun Microelectronics

166

UltraSPARC User’s Manual

BUSY: This bit is set when an interrupt vector is received.

MID<4:0>: Module ID of interrupter.

Note: The BUSY bit must be cleared by software writing zero.

The status of an incoming interrupt can be read from ASI_INTR_RECEIVE. The

BUSY bit is cleared by writing a zero to this register.

Non-privileged access to this register causes a

privileged_action

trap.

9.4 Software Interrupt (SOFTINT) Register

In order to schedule interrupt vectors for processing at a later time, each proces-

sor can send itself signals by setting bits in the SOFTINT Register.

SOFTINT: When set, bits<15:1> cause interrupts at levels IRL<15:1> respectively.

TICK_INT: When TICK_CMPR’s INT_DIS field is cleared (that is, the TICK

interrupt is enabled) and the 63-bit TICK_Compare Register’s

TICK_CMPR field matches the TICK Register’s counter field, the

TICK_INT field is set and a software interrupt is generated. See also

Section 14.1.7, “TICK Register,” on page 239 and Section 14.5.1, “Per-

Processor TICK Compare Field of TICK Register,” on page 249.

The SOFTINT register (ASR 16

16

) is used for communication from (TL > 0) Nucle-

us code to (T=0) kernel code. Non privileged accesses to this register will cause a

privileged_opcode

trap. Interrupt packets and other service requests can be sched-

uled in queues or mailboxes in memory by the nucleus, which then sets SOFT-

INT<n> to cause an interrupt at level <n>. Setting SOFTINT<n> is done via a

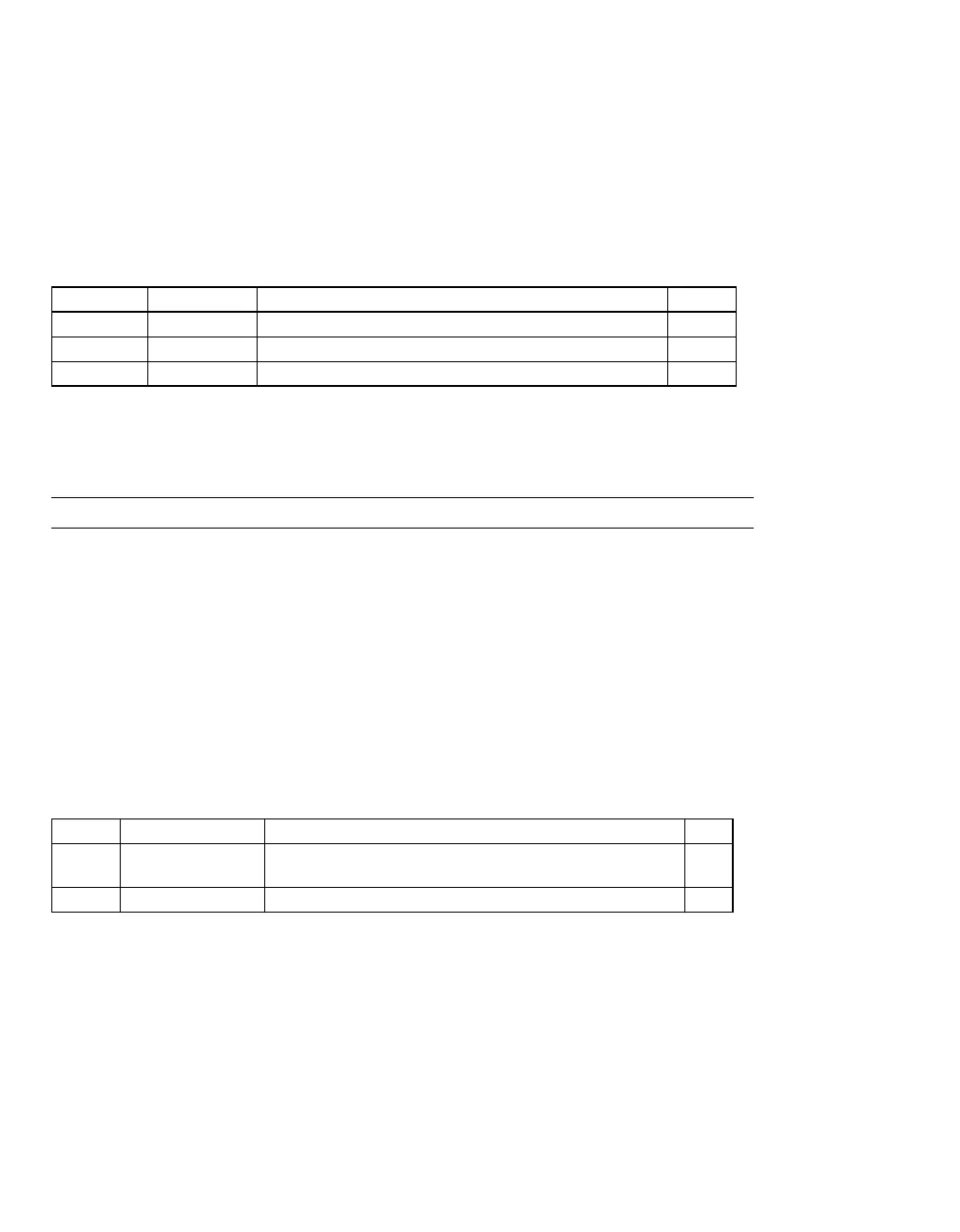

Table 9-4 Interrupt Receive Register Format

Bits Field Use RW

<63:6> Reserved —R

<5> BUSY Set when an interrupt vector is received RW

<4:0> MID<4:0> MID of interrupter R

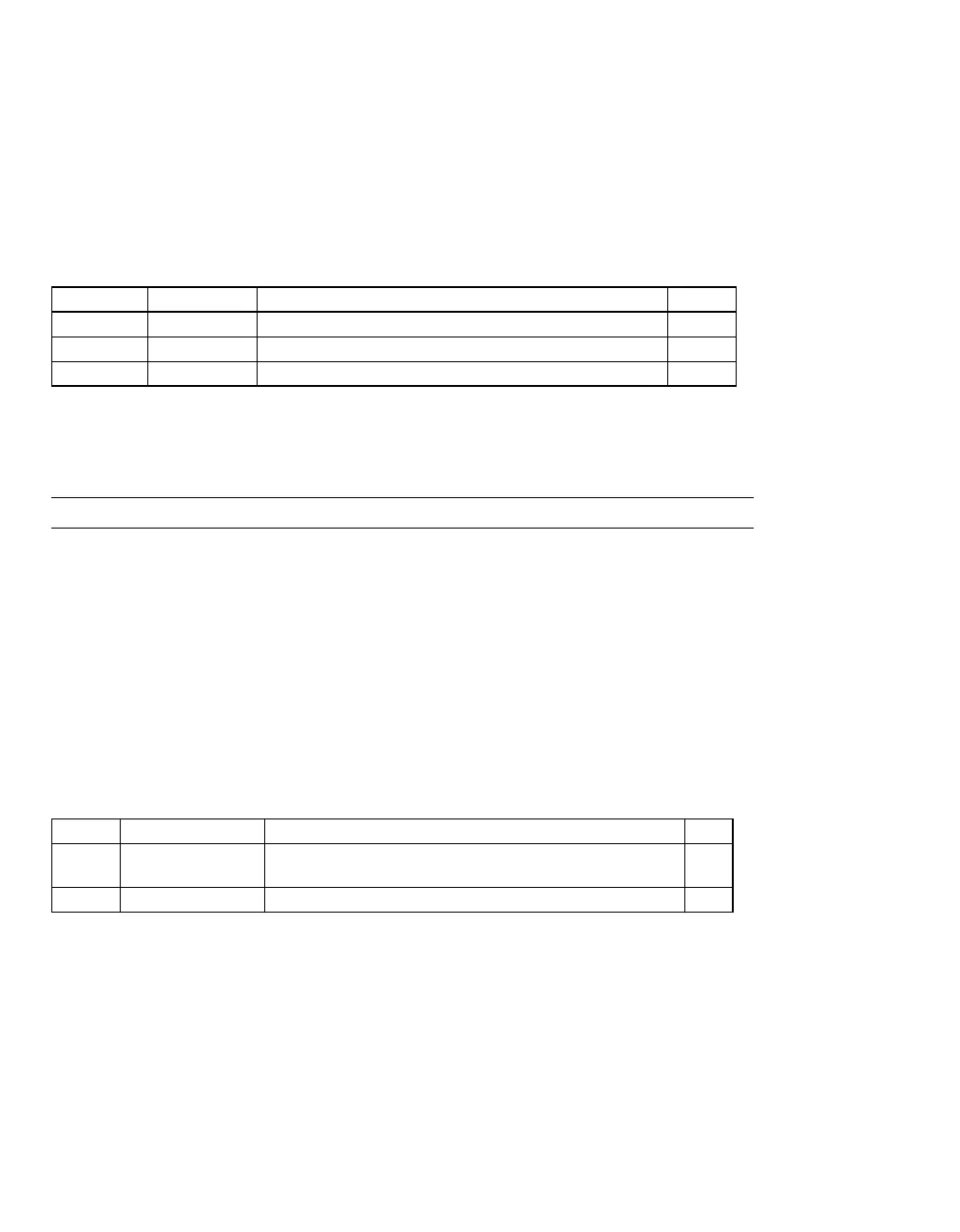

Table 9-5 SOFTINT Register Format

Bits Field Use RW

<15:1> SOFTINT<15:1> When set, bits<15:1> cause interrupts at levels IRL<15:1>

respectively.

RW

<0> TICK_INT Timer interrupt RW

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...