Sun Microelectronics

306

UltraSPARC User’s Manual

DB_VA: The 64-bit virtual data watchpoint address.

Note: UltraSPARC-I and UltraSPARC-II support a 44-bit virtual address space.

Software is responsible to write a sign-extended 64-bit address into the VA

watchpoint register. The watchpoint address is sign-extended to 64 bits from bit

43 when read.

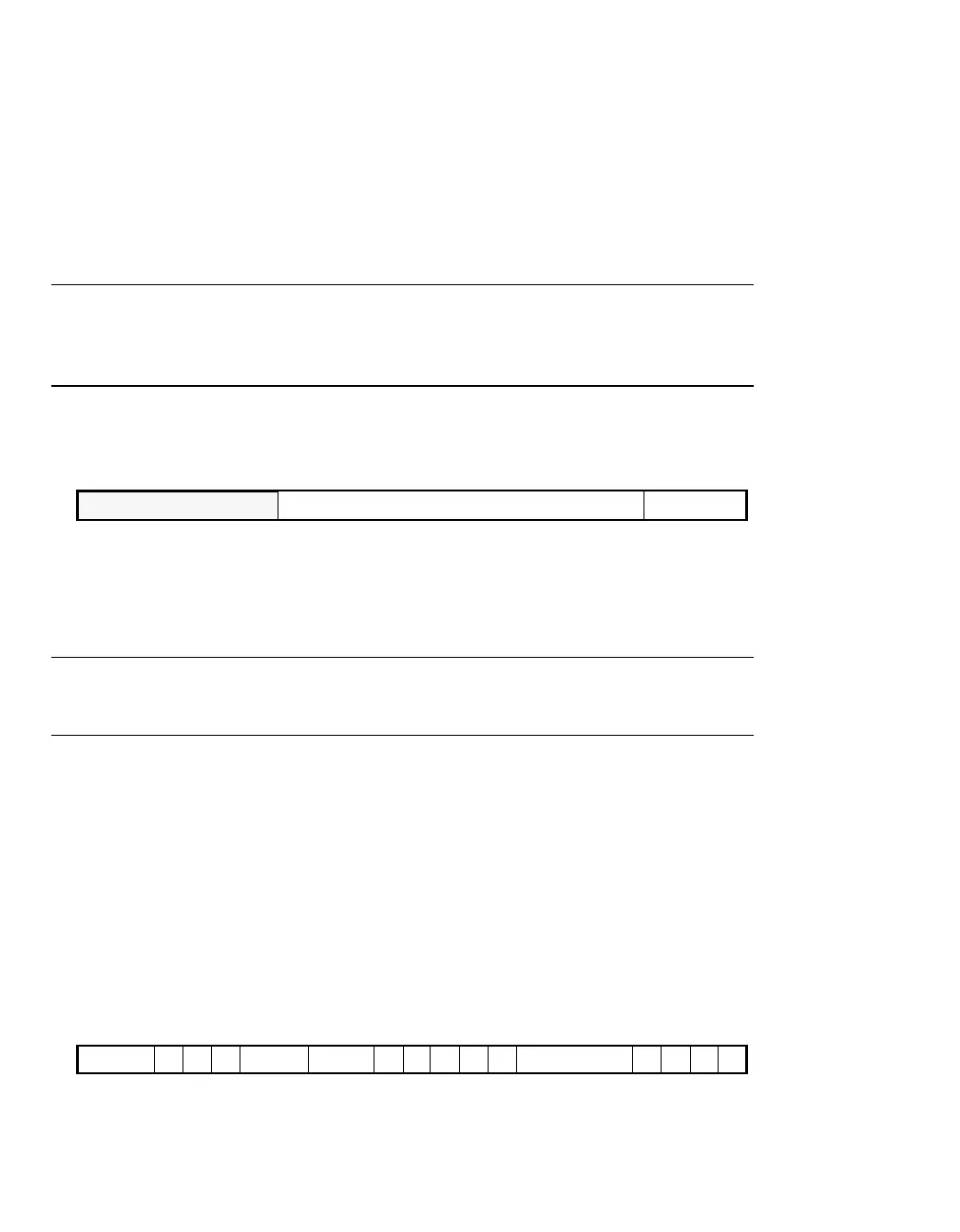

A.5.4 Physical Address Data Watchpoint Register

Figure A-3 PA Data Watchpoint Register Format (ASI 58

16

, VA=40

16

)

DB_PA: The 41-bit physical data watchpoint address.

Note: UltraSPARC-I and UltraSPARC-II support a 41-bit physical address space.

Software is responsible to write a zero-extended 64-bit address into the watch

point register.

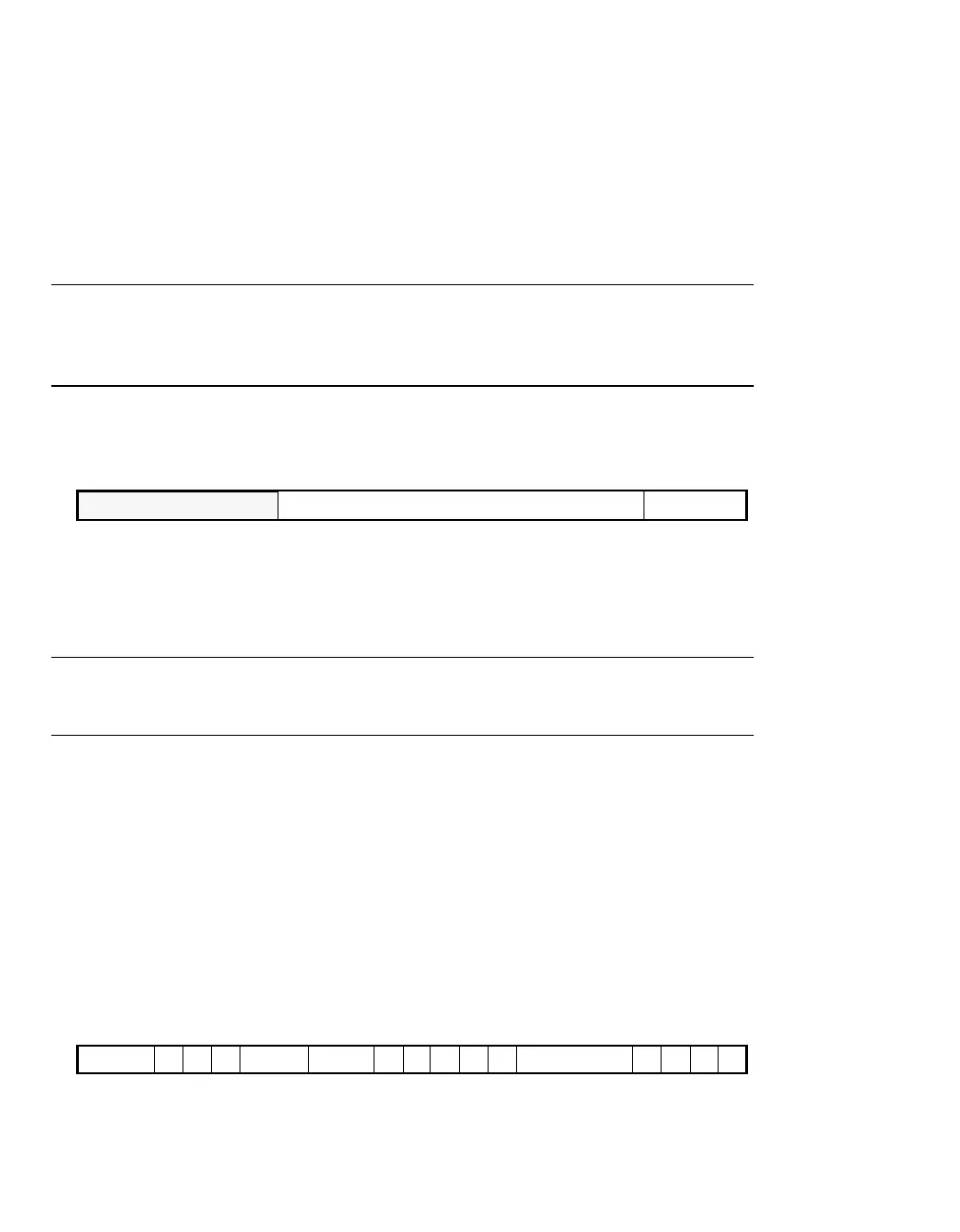

A.6 LSU_Control_Register

ASI 45

16

, VA=00

16

Name: ASI_LSU_CONTROL_REGISTER

• The LSU_Control_Register contains fields that control several memory-related

hardware functions in UltraSPARC. These include I- and D-Caches and

MMUs, bad parity generation, and watchpoint setting. See also Table 10-1,

“Machine State After Reset and in RED_state,” on page 172 for the state of this

register after reset or RED_state trap.

Figure A-4 LSU_Control_Register Access Data Format (ASI 45

16

)

A.6.1 Cache Control

IC: LSU.I-Cache_enable. If cleared, misses are forced on I-Cache accesses

with no cache fill.

63 23041 40

—

DB_PA

63 1920 4 0

— FMPR IC

1

DC

2

IM

3

DM

40

PM

33 32

VM

25 24

PW

23

VR

22

VW

21

—

4144

—

43

—

42

—

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...