Sun Microelectronics

307

A. Debug and Diagnostics Support

DC: LSU.D-Cache_enable. If cleared, misses are forced on D-Cache accesses

with no cache fill. A FLUSH, DONE, or RETRY instruction is needed after

software changes this bit to ensure the new information is used.

A.6.2 MMU Control

IM: LSU.enable_I-MMU. If cleared, the I-MMU is disabled (pass-through

mode).

DM: LSU.enable_D-MMU. If cleared, the D-MMU is disabled (pass-through

mode).

Note: When the MMU/TLB is disabled, a VA is passed through to a PA.

Accesses are assumed to be non-cacheable with side-effects.

A.6.3 Parity Control

FM<15:0> LSU.parity_mask. If set, UltraSPARC writes will generate incorrect

parity on the E-Cache data bus for bytes corresponding to this mask. The

parity_mask corresponds to the 16 bytes of the E-Cache data bus.

Note: The parity mask is endian-neutral.

A.6.4 Watchpoint Control

Watchpoint control is further discussed in Section A.5, “Watchpoint Support,” on

page 304.

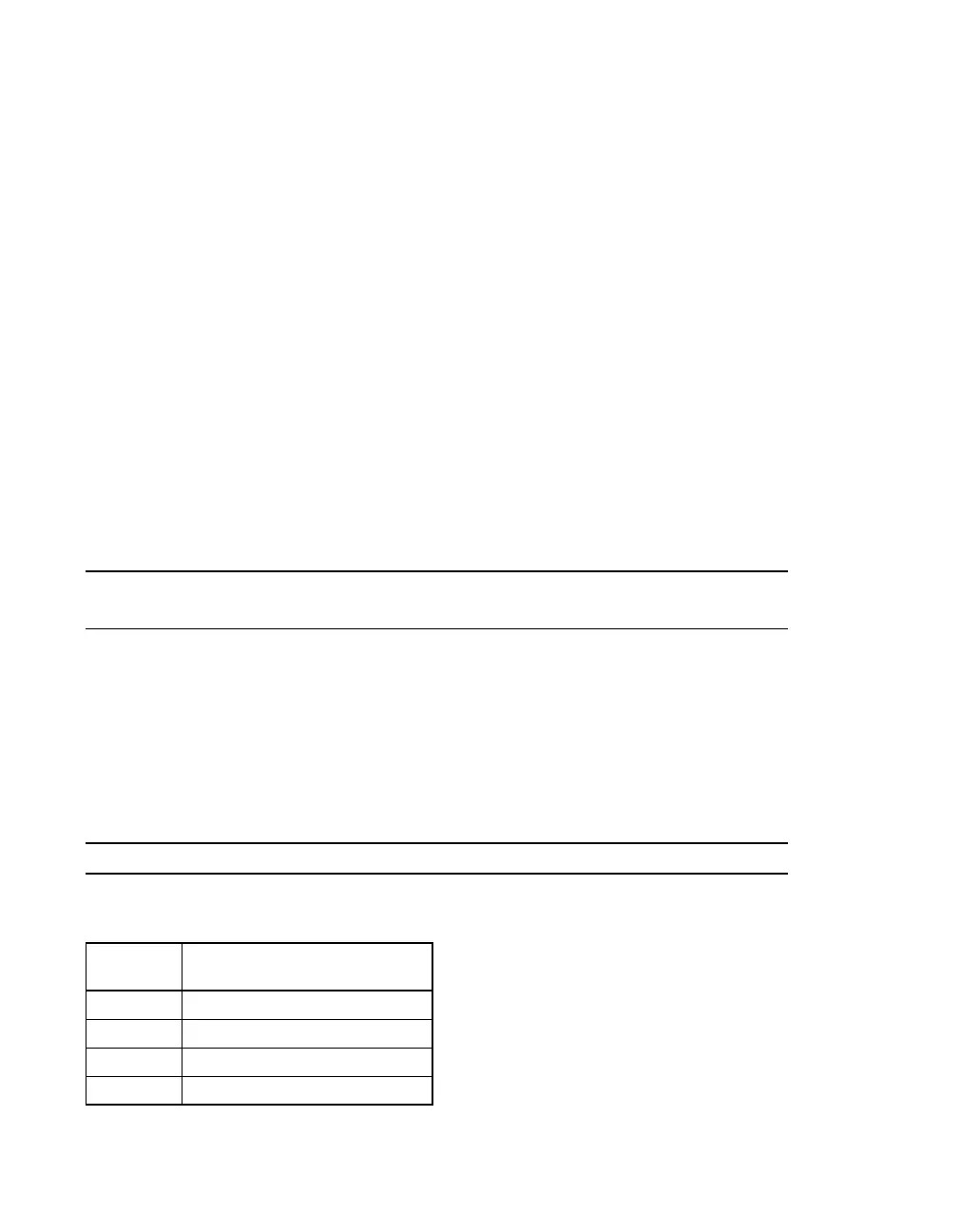

Table A-2 LSU Control Register: Parity Mask Examples

Parity

Mask

Addr of Bytes Affected

FEDC BA98 7654 3210

0000

16

0000 0000 0000 0000

0001

16

0000 0000 0000 0001

2222

16

0010 0010 0010 0010

FFFF

16

1111 1111 1111 1111

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...