Sun Microelectronics

156

UltraSPARC User’s Manual

MID<4:0>: Module (processor) ID register. Identifies the slot in which the

module resides; hardwired to the slot number from the connector pins.

PCAP<16:0>: Processor Capabilities. Shadows the following fields in the

UPA_PORT_ID Register.

• PINT_RDQ<16:15>

• PREQ_DQ<14:9>

• PREQ_RQ<8:5>

• UPACAP<4:0>

8.4 Ancillary State Registers

8.4.1 Overview of ASRs

SPARC-V9 provides up to 32 Ancillary State Registers (ASRs 0..31). ASRs 0..6 are

defined by the SPARC-V9 ISA; ASRs 7..15 are reserved for future use by the ar-

chitecture. ASRs 16..31 are available for use by an implementation.

8.4.2 SPARC-V9-Defined ASRs

Table 8-3 defines the SPARC-V9 ASRs that must be supported by a conforming

processor implementation.

1.

An attempt to read this register by non-privileged software with NPT = 1 causes a

privileged_action

trap. The tick

register can only be written with the privileged wrpr instruction.

2.

Read-only—an attempt to write this register causes an

illegal_instruction

trap.

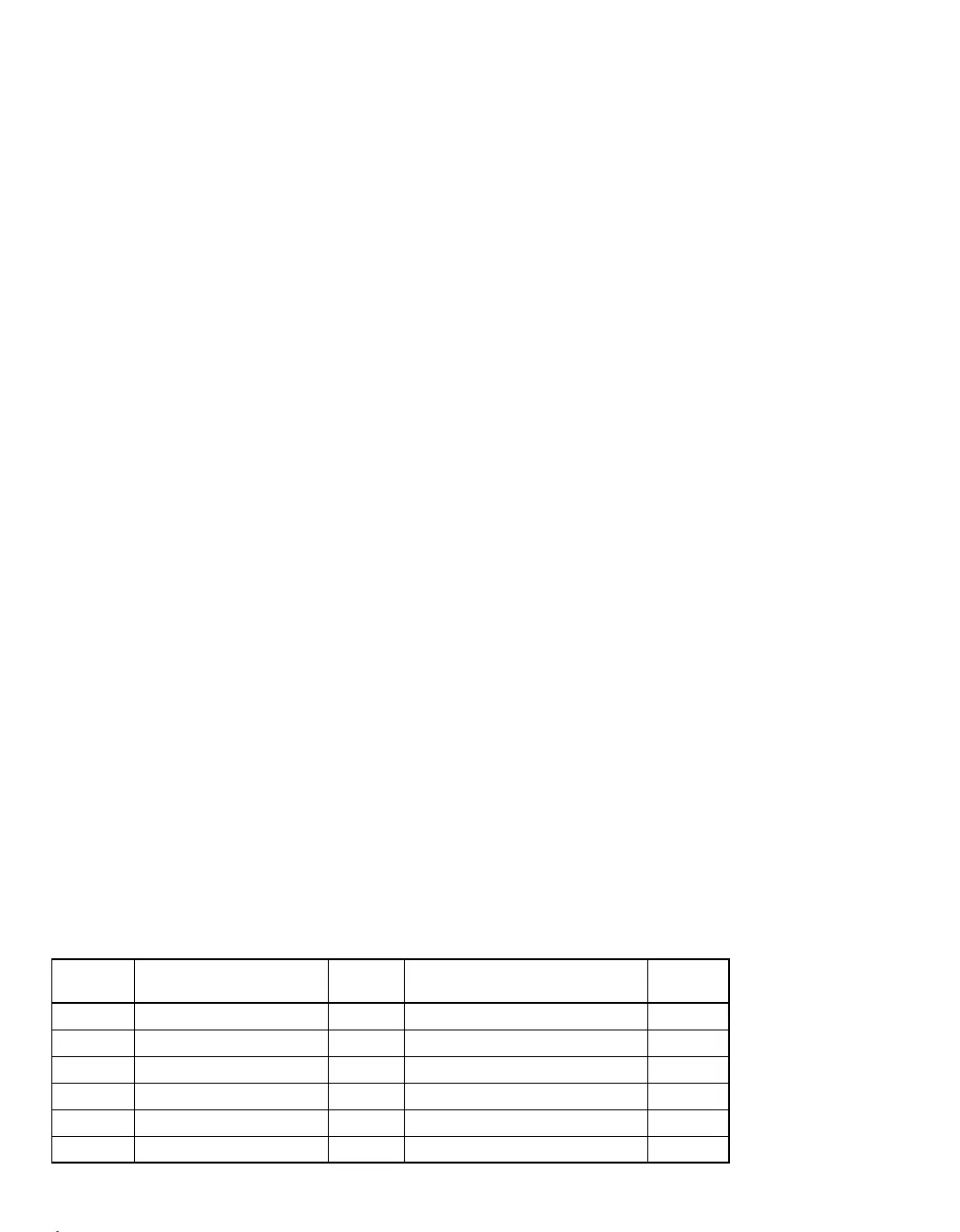

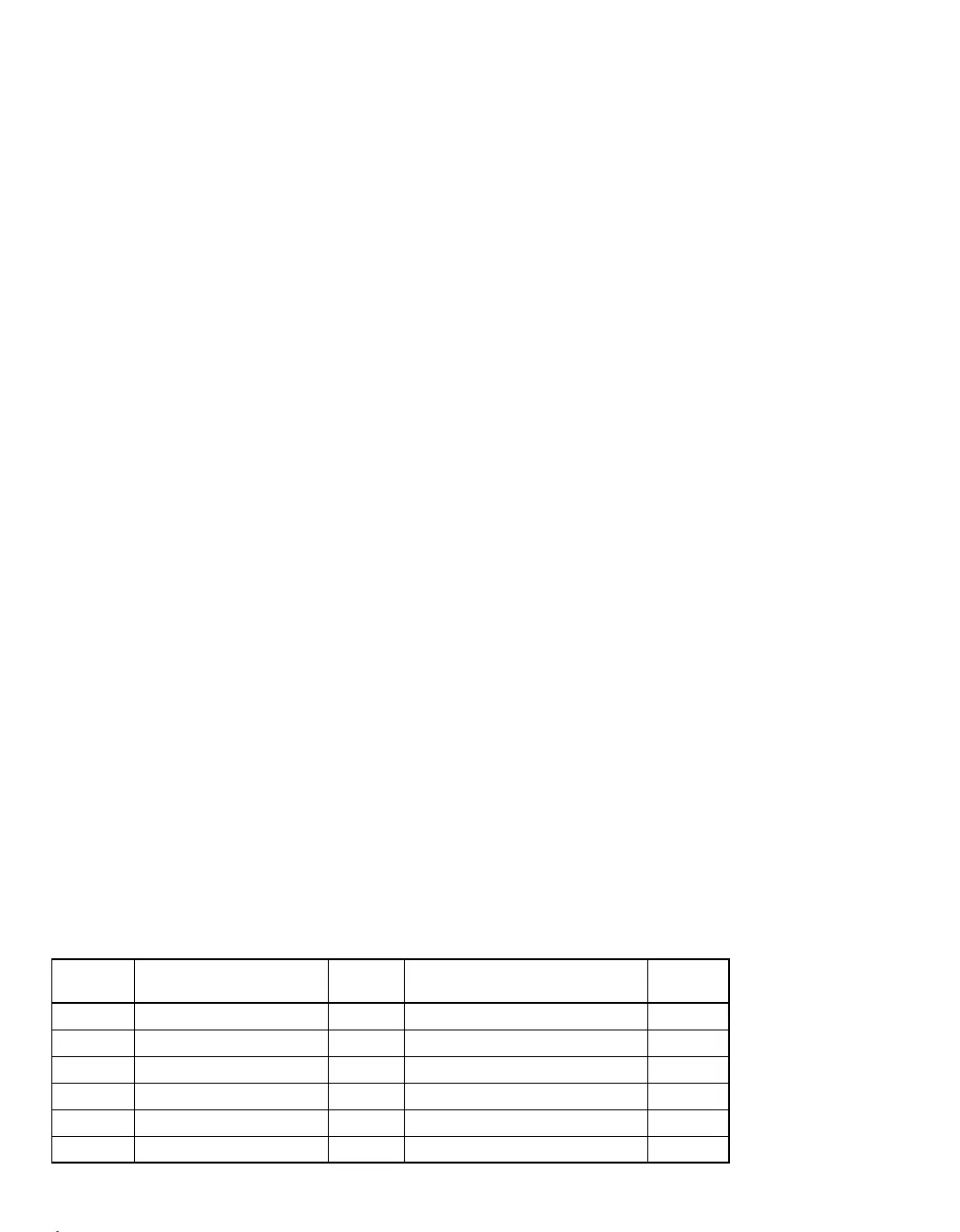

Table 8-3 Mandatory SPARC-V9 ASRs

ASR

Value

ASR Name Access Description Section

00

16

Y_REG

RW

Y register

V9

02

16

COND_CODE_REG

RW

Condition code register

V9

03

16

ASI_REG

RW

ASI register

V9

04

16

TICK_REG

R

1,2

TICK register

V9

05

16

PC

R

2

Program Counter

V9

06

16

FP_STATUS_REG

RW

Floating-point status register

V9

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...