Sun Microelectronics

157

8. Address Spaces, ASIs, ASRs, and Traps

8.4.3 Non-SPARC-V9 ASRs

Non-SPARC-V9 ASRs are listed in Table 8-4 on page 157.

1.

Read accesses cause an

illegal_instruction

trap. Nonprivileged write accesses cause a

privileged_opcode

trap.

2.

Accesses cause an

fp_disabled

trap if PSTATE.PEF or FPRS.FEF are zero.

3.

Nonprivileged accesses cause a

privileged_opcode

trap.

4.

Nonprivileged accesses with PCR.PRIV=0 cause a

privileged_action

trap.

Suggested Assembly Language Syntax

rd %y, reg

rd

wr reg

rs1

,reg_or_imm, %y

rd %ccr, reg

rd

wr reg

rs1

,reg_or_imm, %ccr

rd %asi, reg

rd

wr reg

rs1

,reg_or_imm, %asi

rd %tick, reg

rd

rd %pc reg

rd

rd %fprs, reg

rd

wr reg

rs1

,reg_or_imm, %fprs

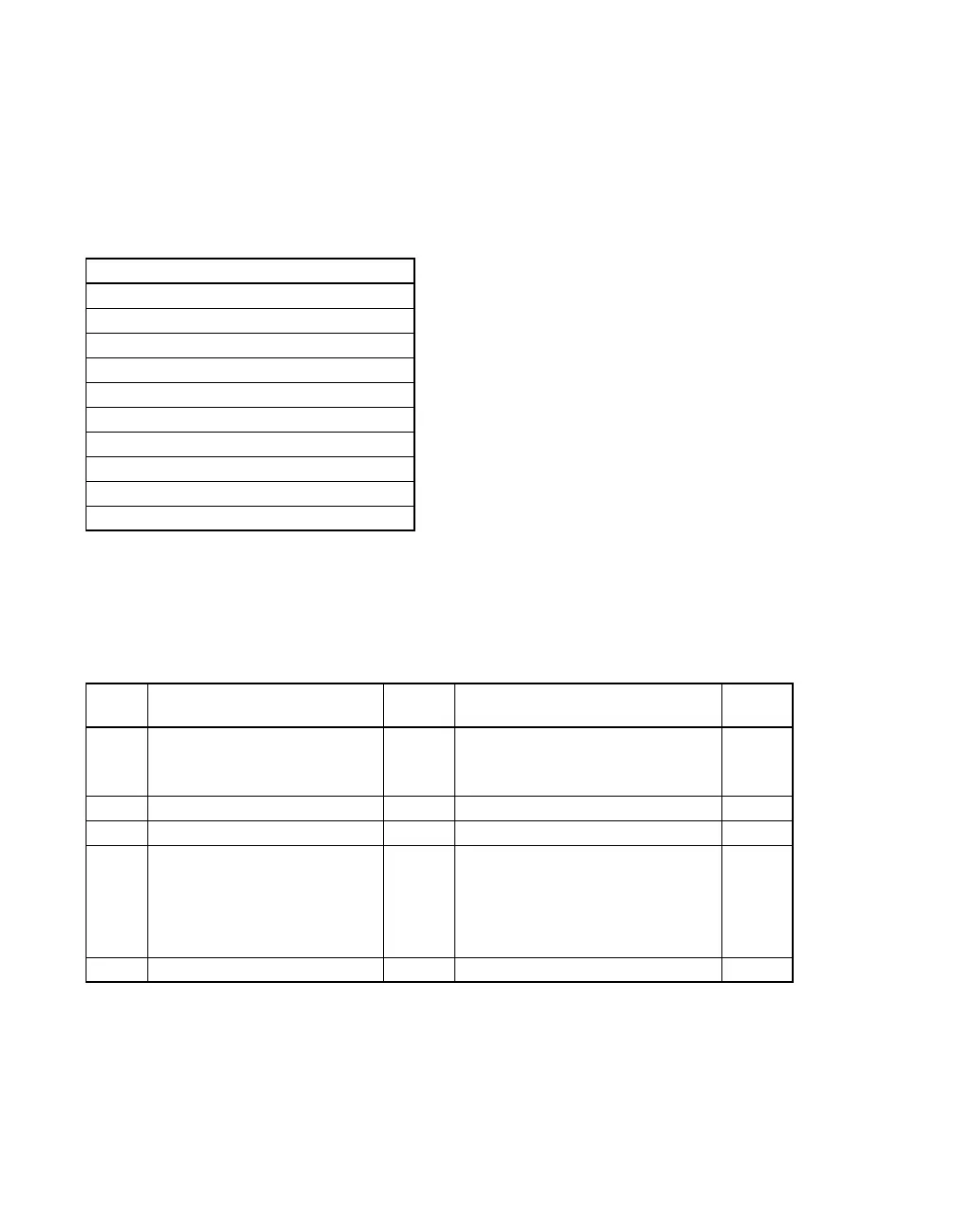

Table 8-4 Non-SPARC-V9 ASRs

ASR

Value

ASR Name/Syntax Access Description Section

10

16

PERF_CONTROL_REG RW

3

Performance Control Reg (PCR) B.2

11

16

PERF_COUNTER RW

4

Performance Instrumentation

Counters (PIC)

B.4

12

16

DISPATCH_CONTROL_REG RW

3

Dispatch Control Register (DCR) A.3

13

16

GRAPHIC_STATUS_REG RW

2

Graphics Status Register (GSR) 13.4

14

16

SET_SOFTINT W

1

Set bit(s) in per-processor Soft

Interrupt register

9.4

15

16

CLEAR_SOFTINT W

1

Clear bit(s) in per-processor Soft

Interrupt register

9.4

16

16

SOFTINT_REG RW

3

Per-processor Soft Interrupt register 9.4

17

16

TICK_CMPR_REG RW

3

TICK compare register 14.5.1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...