Sun Microelectronics

41

MMU Internal Architecture 6

6.1 Introduction

This chapter provides detailed information about the UltraSPARC Memory Man-

agement Unit. It describes the internal architecture of the MMU and how to pro-

gram it.

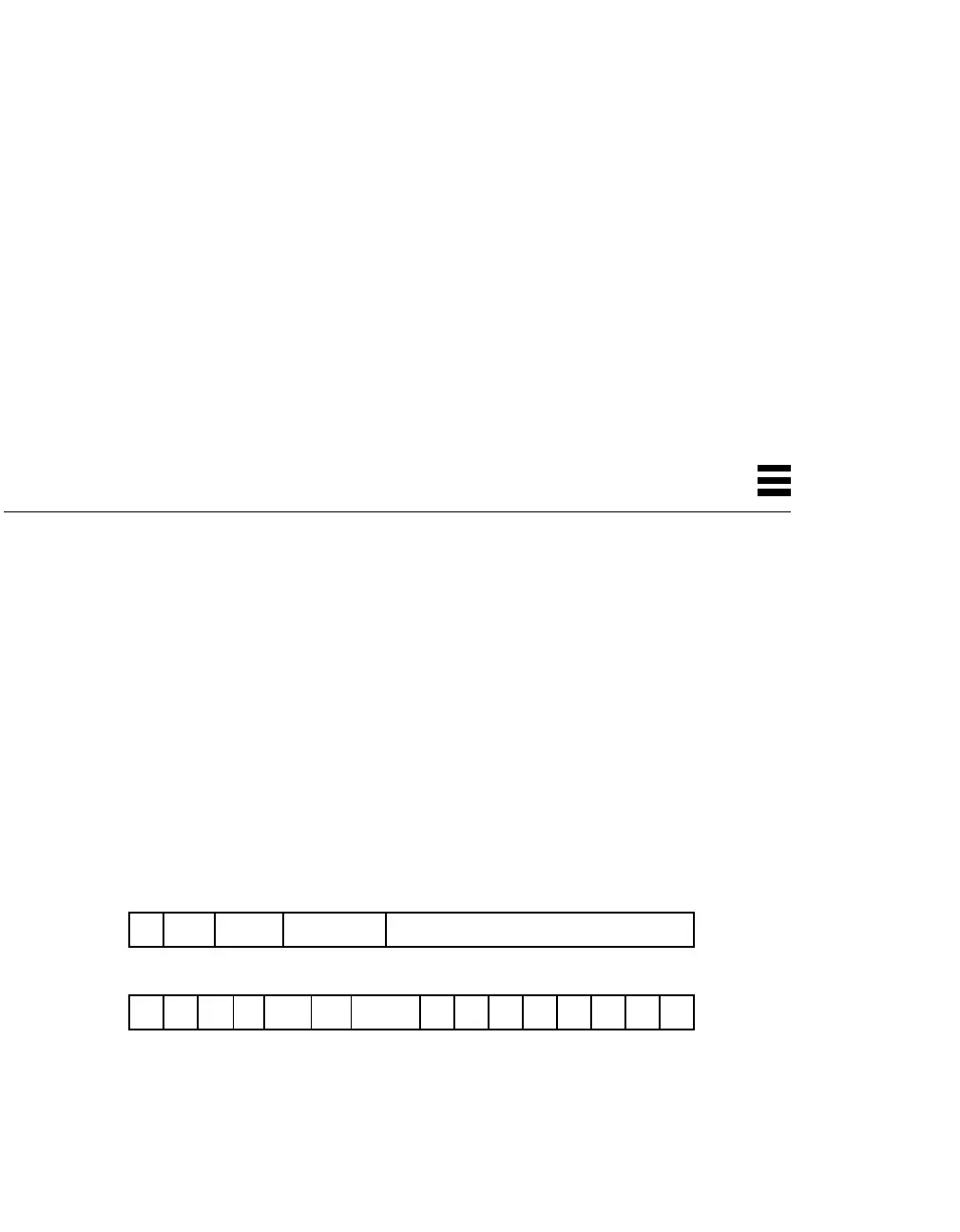

6.2 Translation Table Entry (TTE)

The Translation Table Entry, illustrated in Figure 6-1, is the UltraSPARC equiva-

lent of a SPARC-V8 page table entry; it holds information for a single page map-

ping. The TTE is broken into two 64-bit words, representing the tag and data of

the translation. Just as in a hardware cache, the tag is used to determine whether

there is a hit in the TSB. If there is a hit, the data is fetched by software.

Figure 6-1 Translation Table Entry (TTE) (from TSB)

G: Global. If the Global bit is set, the Context field of the TTE is ignored

during hit detection. This allows any page to be shared among all (user

or supervisor) contexts running in the same processor. The Global bit is

duplicated in the TTE tag and data to optimize the software miss handler.

Context: The 13-bit context identifier associated with the TTE.

G VA_tag<63:22>Context

063

Tag

Data

414248 47

—

62 6061

—

PA<40:13>Size Soft

011363 41

CVCP

2312

WP

4

Diag

61 6062 5

GV E

6

L

7

Soft2

5059

NFO

49 40

IE

58

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...