Sun Microelectronics

198

UltraSPARC User’s Manual

RDASR format:

WRASR format:

Accesses to this register cause an

fp_disabled

trap if either PSTATE.PEF or

FPRS.FEF is zero.

Figure 13-2 shows the format of the GSR.

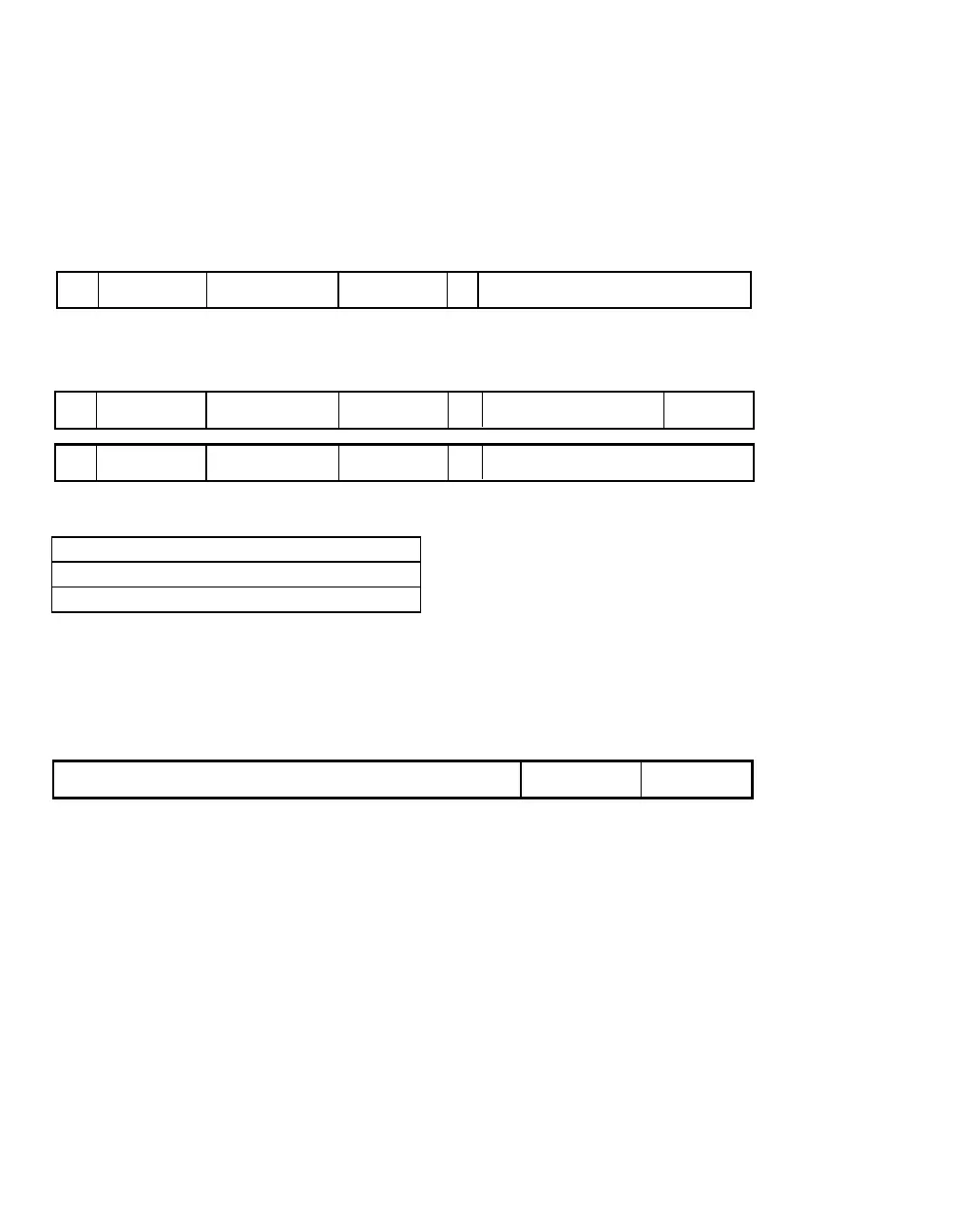

Figure 13-2 GSR Format (ASR 10

16

)

scale_factor: Shift count in the range 0..15, used by PACK instructions for pixel

formatting.

alignaddr_offset: Least significant three bits of the address computed by the last

ALIGNADDRESS or ALIGNADDRESS_LITTLE instruction. See Section 13.5.5,

“Alignment Instructions,” on page 214.

Traps:

fp_disabled

13.5 Graphics Instructions

All instruction operands are in floating-point registers, unless otherwise speci-

fied. This provides the maximum number of registers (32 double-precision) and

the maximum instruction parallelism (for example, UltraSPARC is four scalar for

Suggested Assembly Language Syntax

rd %gsr,

reg

rd

wr

reg

rs1

,

reg_or_imm

, %gsr

10 op3 —rd rs1

31 141924 18 13 02530 29

i=0

12

10 op3 simm13rd rs1

31 141924 18 13 02530 29

12

i=1

10 op3 —rd rs1

i=0

rs2

5

4

alignaddr_offset

63 02

scale_factor

3

—

67

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...