Sun Microelectronics

199

13. UltraSPARC Extended Instructions

floating-point/graphics code only). Pixel values are stored in single-precision

floating point registers and fixed values are stored in double-precision floating-

point registers, unless otherwise specified.

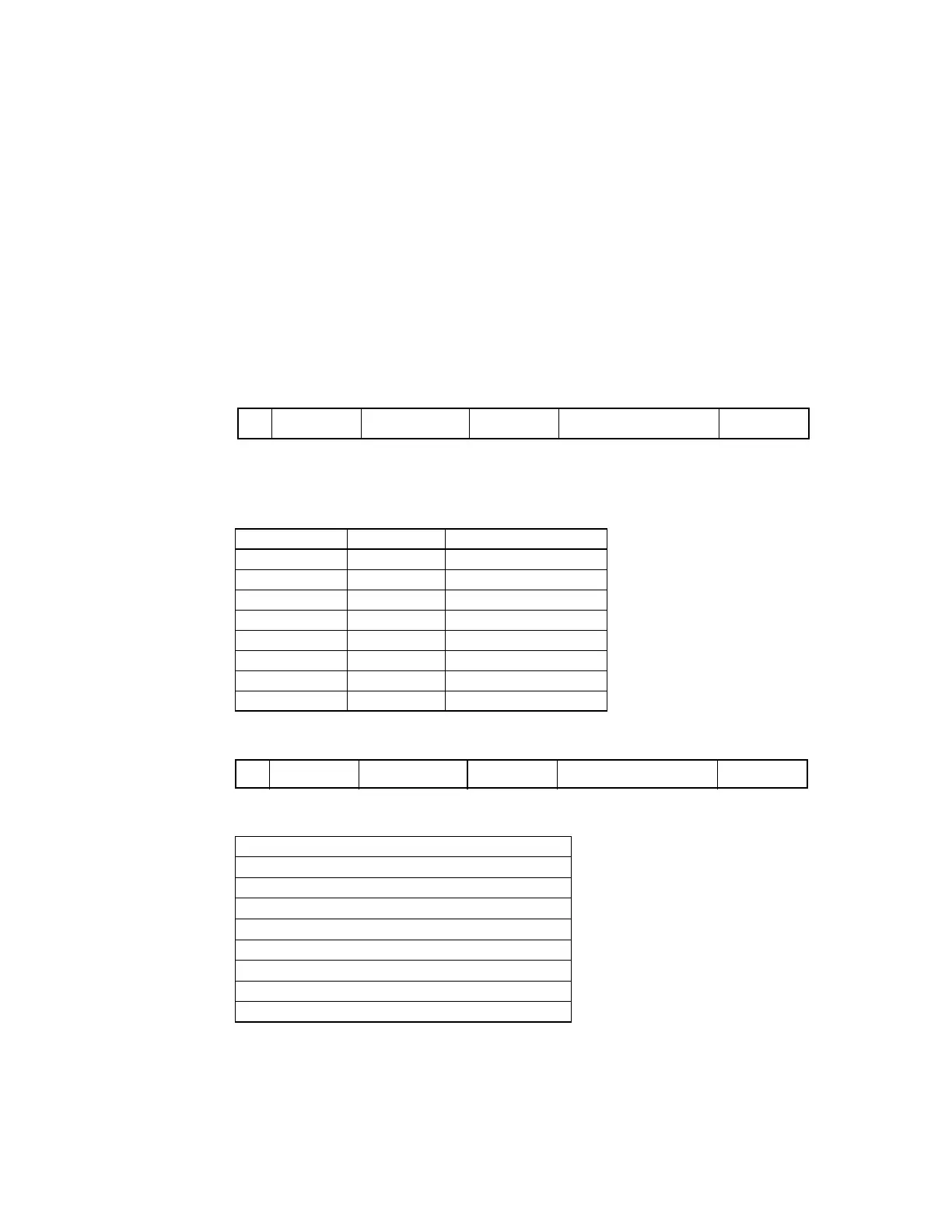

13.5.1 Opcode Format

The graphics instruction set maps to the opcode space reserved for the Imple-

mentation-Dependent Instruction 1 (IMPDEP1) instructions.

Format (3):

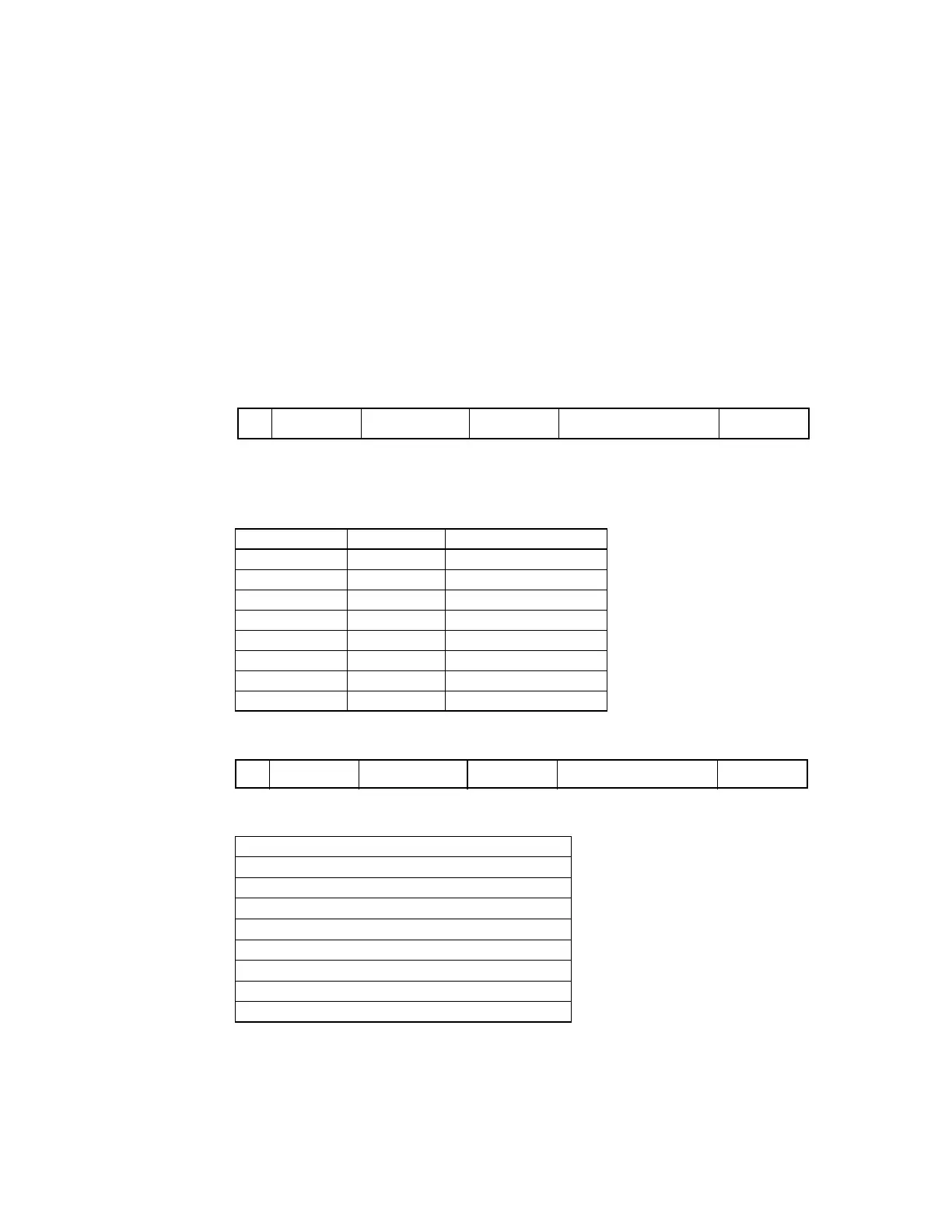

13.5.2 Partitioned Add/Subtract Instructions

Format (3):

opcode opf operation

FPADD16

0 0101 0000

Four 16-bit add

FPADD16 S

0 0101 0001

Two 16-bit add

FPADD32

0 0101 0010

Two 32-bit add

FPADD32S

0 0101 0011

One 32-bit add

FPSUB16

0 0101 0100

Four 16-bit subtract

FPSUB16S

0 0101 0101

Two 16-bit subtract

FPSUB32

0 0101 0110

Two 32-bit subtract

FPSUB32S

0 0101 0111

One 32-bit subtract

Suggested Assembly Language Syntax

fpadd16

freg

rs1

,

freg

rs2

,

freg

rd

fpadd16s

freg

rs1

,

freg

rs2

,

freg

rd

fpadd32

freg

rs1

,

freg

rs2

,

freg

rd

fpadd32s

freg

rs1

,

freg

rs2

,

freg

rd

fpsub16

freg

rs1

,

freg

rs2

,

freg

rd

fpsub16s

freg

rs1

,

freg

rs2

,

freg

rd

fpsub32

freg

rs1

,

freg

rs2

,

freg

rd

fpsub32s

freg

rs1

,

freg

rs2

,

freg

rd

10 110110 rs2rd rs1

31 141924 18 13 02530 29 4

opf

5

10 110110 rs2rd rs1

31 141924 18 13 02530 29 4

opf

5

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...