Sun Microelectronics

10

UltraSPARC User’s Manual

1.3.10 Memory Interface Unit (MIU)

The MIU handles all transactions to the system controller; for example, external

cache misses, interrupts, snoops, writebacks, and so on. The MIU communicates

with the system at some model-dependent fraction of the UltraSPARC frequency.

Table 1-5 shows the possible ratios between the processor and system clock fre-

quencies for each UltraSPARC model.

1.4 UltraSPARC Subsystem

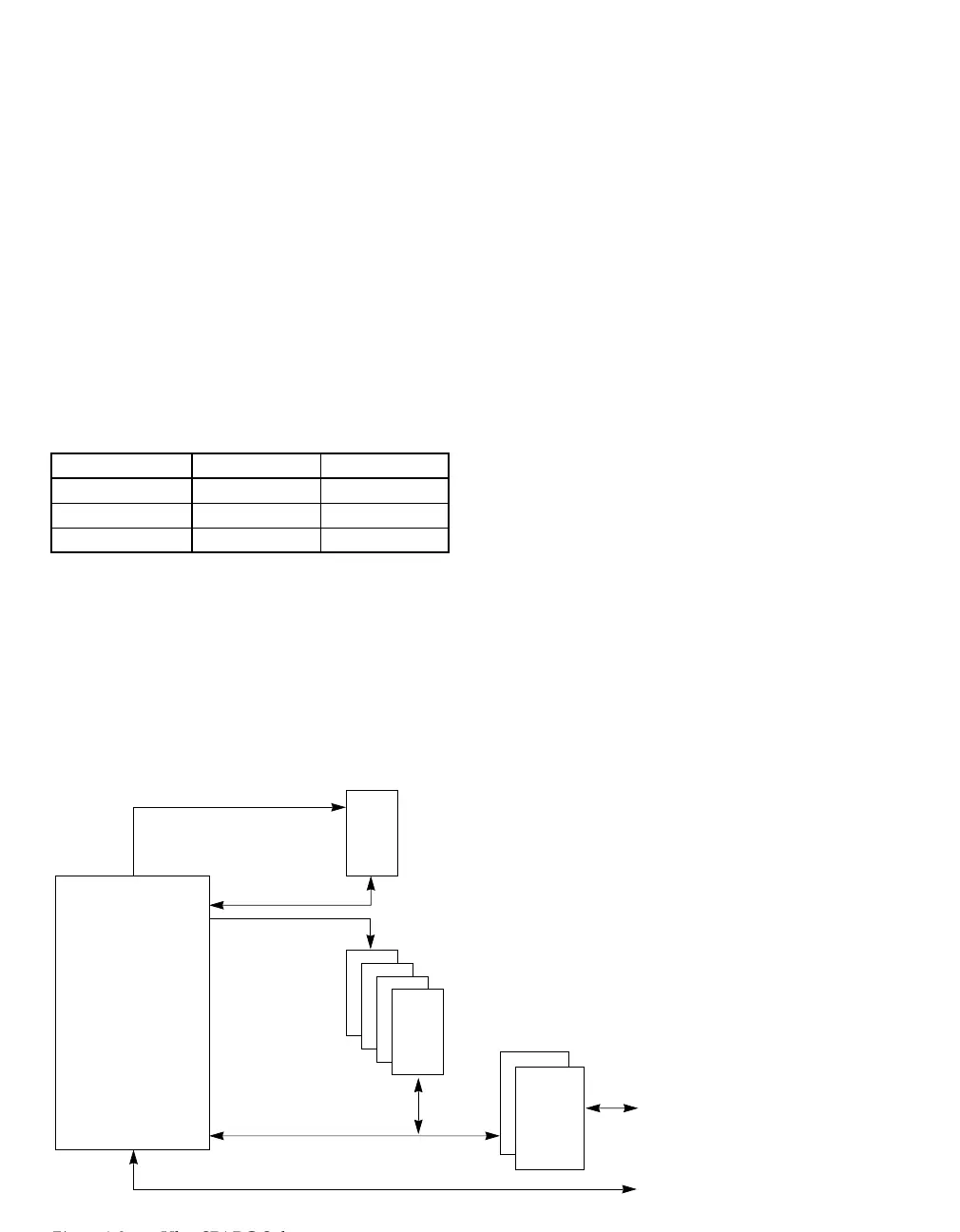

Figure 1-2 shows a complete UltraSPARC subsystem, which consists of the

UltraSPARC processor, synchronous SRAM components for the E-Cache tags and

data, and two UltraSPARC Data Buffer (UDB) chips. The UDBs isolate the

E-Cache from the system, provide data buffers for incoming and outgoing system

transactions, and provide ECC generation and checking.

Figure 1-2 UltraSPARC Subsystem

Table 1-5 Model-Dependent Processor : System Clock Frequency Ratios

Frequency Ratio UltraSPARC-I UltraSPARC-II

2 : 1 ✓✓

3 : 1 ✓✓

4 : 1 ✓

E-Cache Data SRAM

UDB

E-Cache Tag SRAM

System

Data Bus

System

Address Bus

E-Cache Data

Tag Data

Tag Address

Data Address

UltraSPARC

Processor

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...