Sun Microelectronics

11

Processor Pipeline 2

2.1 Introductions

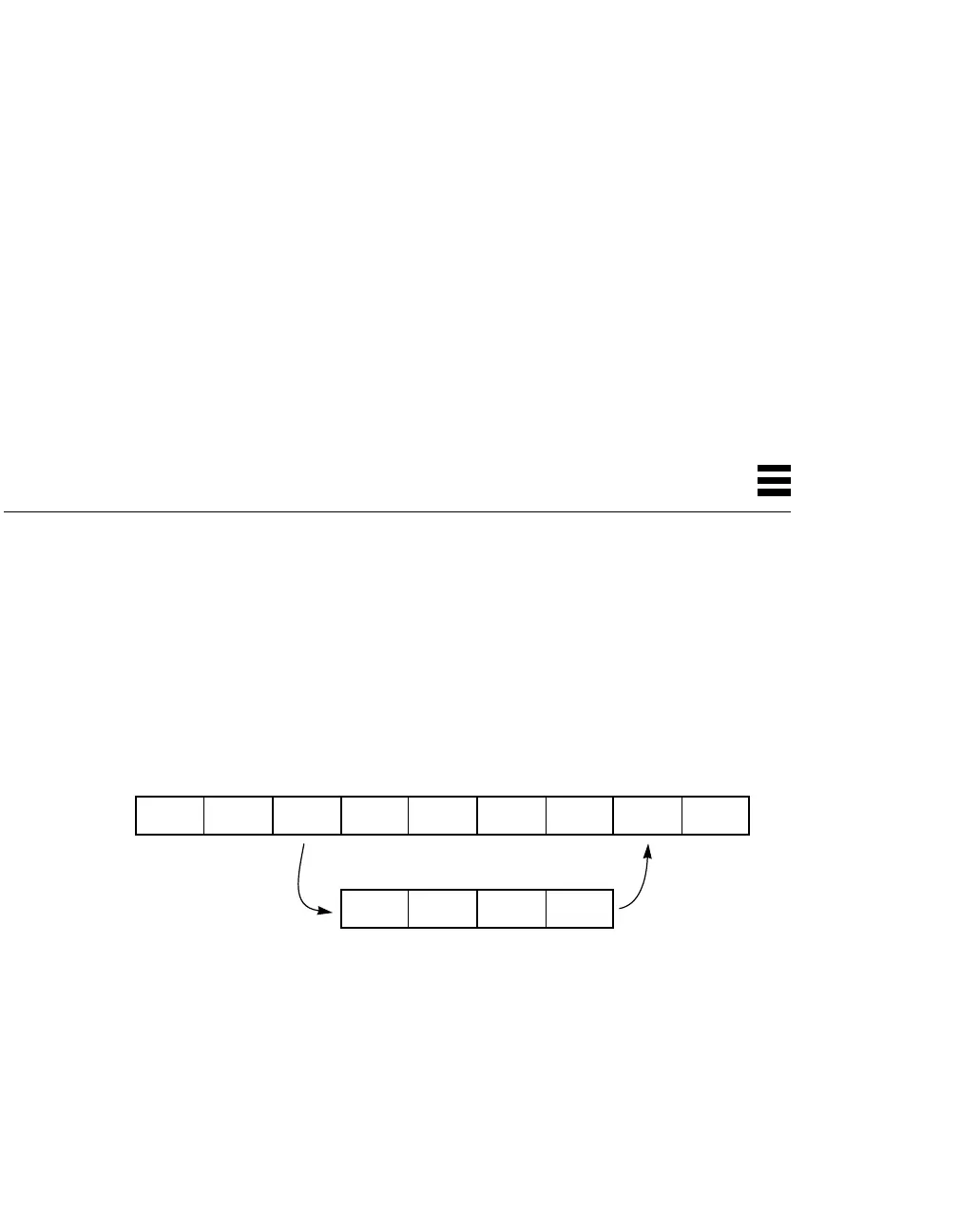

UltraSPARC contains a 9-stage pipeline. Most instructions go through the pipe-

line in exactly 9 stages. The instructions are considered terminated after they go

through the last stage (W), after which changes to the processor state are irrevers-

ible. Figure 2-1 shows a simplified diagram of the integer and floating-point pipe-

line stages.

Figure 2-1 UltraSPARC Pipeline Stages (Simplified)

Three additional stages are added to the integer pipeline to make it symmetrical

with the floating-point pipeline. This simplifies pipeline synchronization and ex-

ception handling. It also eliminates the need to implement a floating-point queue.

Floating-point instructions with a latency greater than three (divide, square root,

and inverse square root) behave differently than other instructions; the pipe is

“extended” when the instruction reaches stage N

1

. See Chapter 16, “Code Gener-

ation Guidelines” for more information. Memory operations are allowed to pro-

ceed asynchronously with the pipeline in order to support latencies longer than

the latency of the on-chip D-Cache.

Fetch Decode Group Execute Cache N

1

N

2

N

3

Write

Integer Pipeline

Register X

1

X

2

X

3

Floating-Point &

Graphics Pipeline

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...