Sun Microelectronics

97

7. UltraSPARC External Interfaces

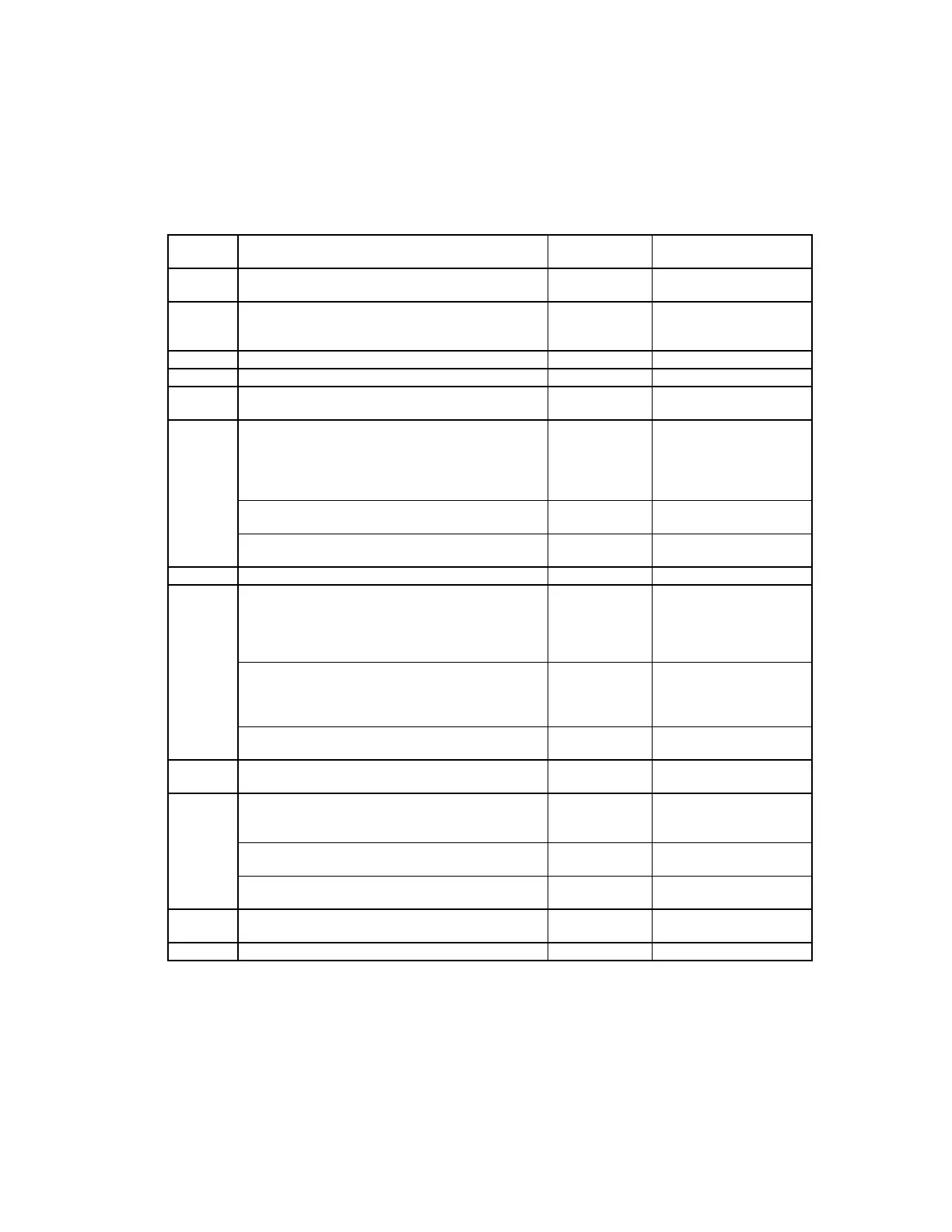

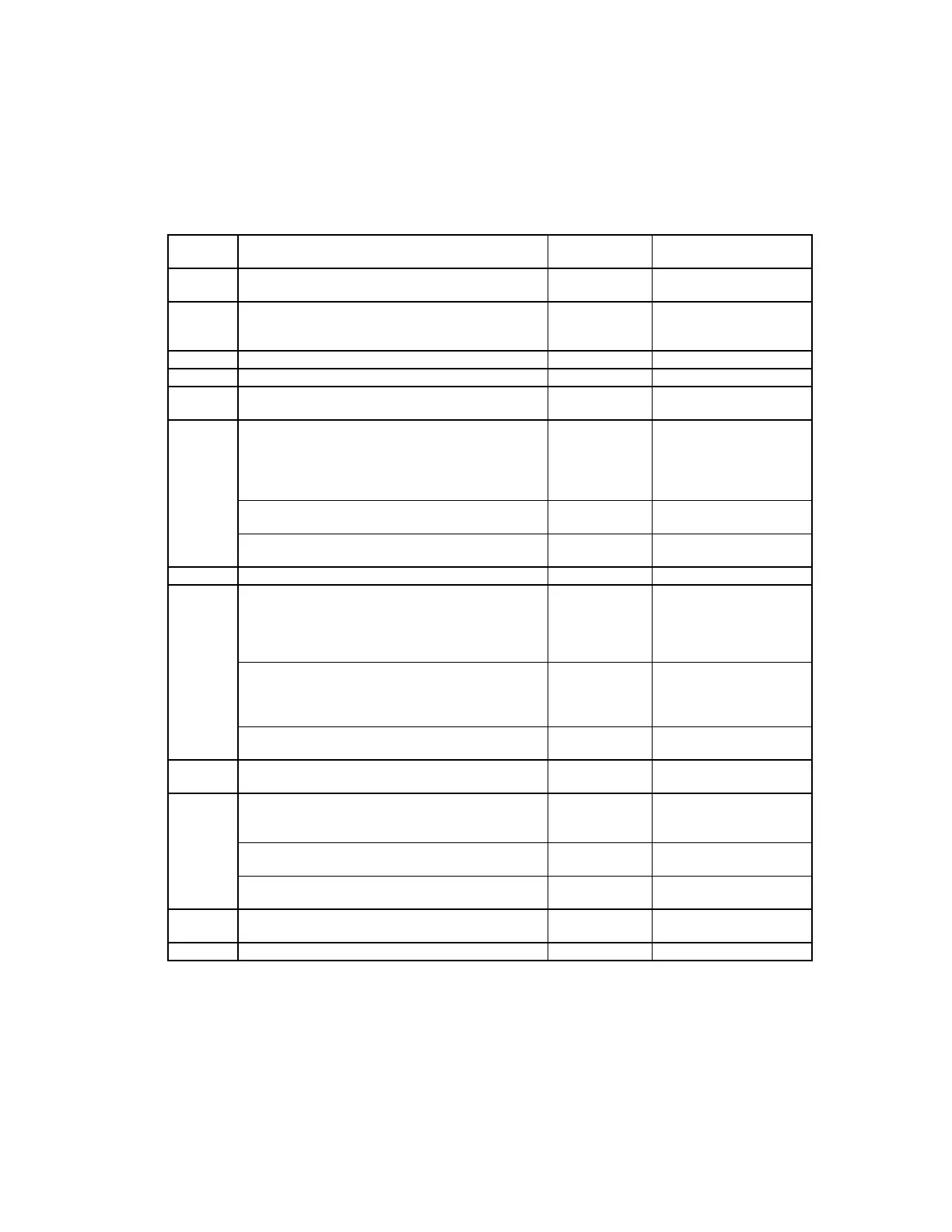

Table 7-9 Transitions Allowed for Cache Coherence Protocol

Transition Description

Transaction Req

to/from Port

Acknowledgment

I → E Load miss; data coming from memory to an invalid

line (no other cache has the data).

P_RDS_REQ S_RBU

I → S Load miss; data provided by another cache or memory

to an invalid line (another cache has the data)

I-Cache miss or PREFETCH.

P_RDS_REQ

P_RDSA_REQ

S_RBS

S_RBS

I → M Store miss, atomic miss on invalid line, PREFETCH. P_RDO_REQ S_RBU

E → M Store hit or atomic hit to Exclusive Clean line. No Transaction No Transaction

E → S Request from system to share this line (load miss from

another processor).

S_CPB_REQ,

S_CPB_MSI_REQ

P_SACK | P_SACKD

followed by S_CRAB

E → I i) A clean line is victimized by the processor.

I-Cache miss.

Write miss.

P_RDS_REQ

or

P_RDSA_REQ

or

P_RDO_REQ

S_RBU or S_RBS

S_RBS

S_RBU

ii) Request from system to copyback and invalidate

this line (store miss from another processor).

S_CPI_REQ P_SACK|P_SACKD

followed by S_CRAB

iii) Request from SC to invalidate this line (block store

from another processor)

S_INV_REQ P_SACK|P_SACKD

S → M Store hit, atomic hit to Shared Clean line, PREFETCH. P_RDO_REQ S_OAK

S

→ I i) A Shared Clean line is victimized by UltraSPARC.

I-Cache miss.

Write hit on shared line.

P_RDS_REQ

or

P_RDSA_REQ

or

P_RDO_REQ

S_RBU or S_RBS

S_RBS

S_RBU

ii) Another processor wants to write this shared line. S_INV_REQ

or

S_CPI_REQ

P_SACK|P_SACKD

P_SACK|P_SACKD

followed by S_CRAB

iii) Request from SC to invalidate this line (block store

from another processor).

S_INV_REQ P_SACK|P_SACKD

M

→ O Request from another processor to read a modified

line, memory is not updated (as opposed to M → S).

S_CPB_REQ P_SACK|P_SACKD

followed by S_CRAB

M, O

→ I

i) A Modified line is victimized by the processor

(Writeback).

P_WRB_REQ S_WAB or S_WBCAN

if system takes ownership

before completing Writeback

ii) Request from system to copyback and invalidate

this line (store miss from another processor).

S_CPI_REQ P_SACK|P_SACKD

followed by S_CRAB

iii) Request from system to invalidate this line (block

store from another processor)

S_INV_REQ P_SACK|P_SACKD

M, O

→ S Request from another processor to read this line, mem-

ory is updated so line becomes clean (c.f. M → O)

S_CPB_MSI_REQ P_SACK|P_SACKD

followed by S_CRAB

O

→ M Store hit, atomic hit to Modified line, PREFETCH. P_RDO_REQ S_OAK

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...