Sun Microelectronics

99

7. UltraSPARC External Interfaces

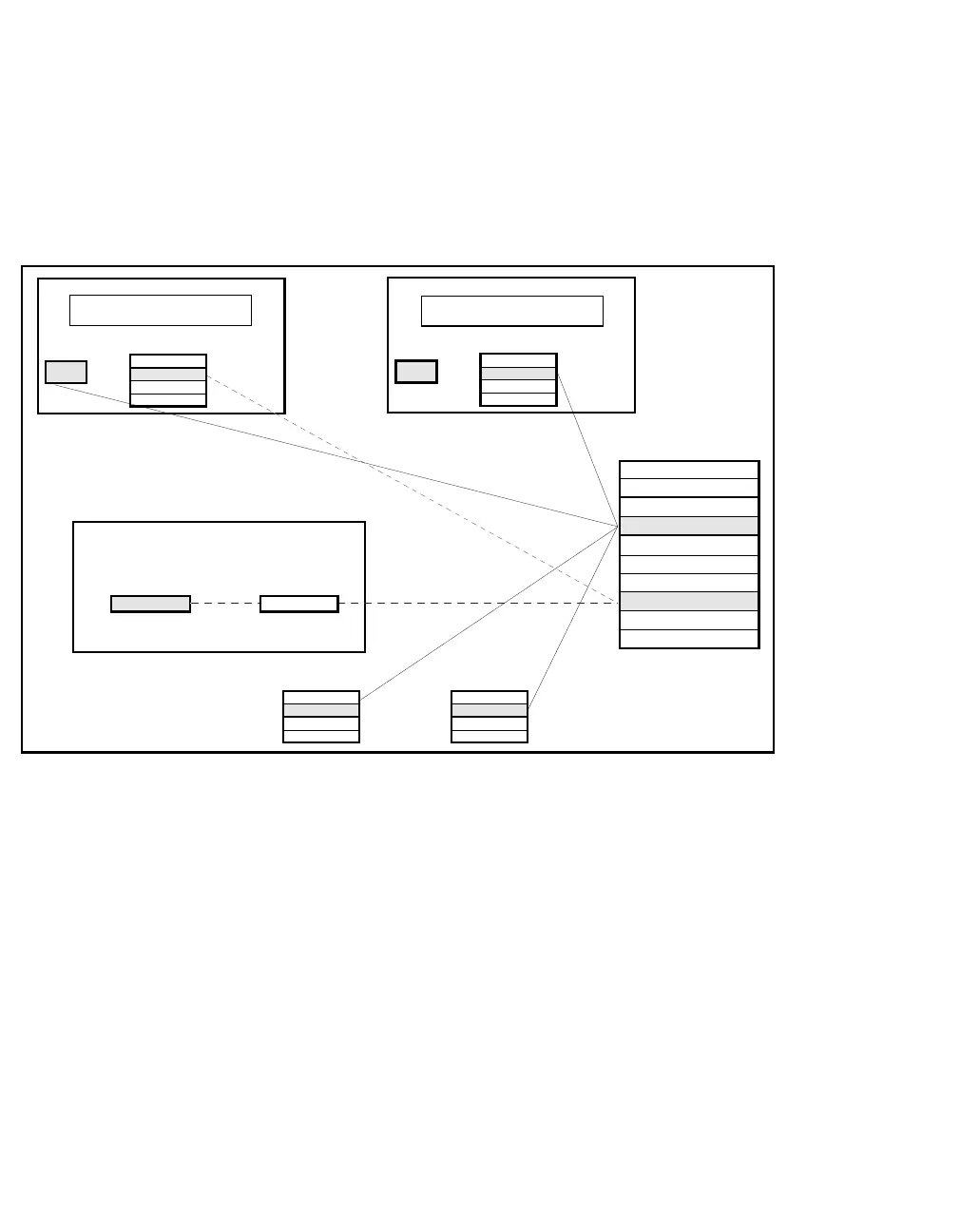

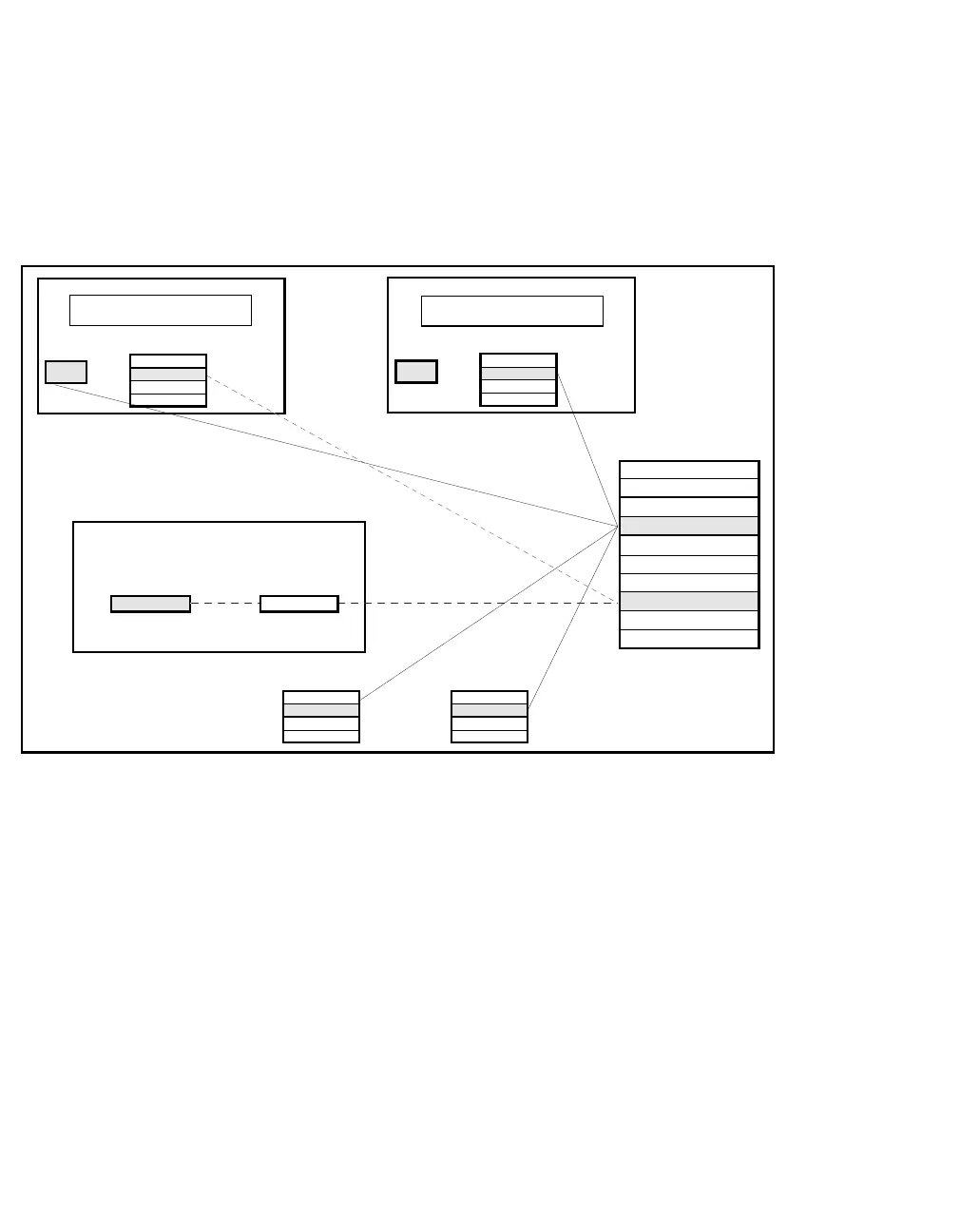

Figure 7-21 Cache Coherence Model Using Centralized Duplicate Tags (Dtags)

In the example shown in Figure 7-21, two UltraSPARCs cache the same data

block A. UltraSPARC

1

has block A in the O state; UltraSPARC

k

has block A in the

S state. UltraSPARC

1

victimizes block A for a new data block B, and transfers the

dirty block A to the writeback buffer for writing to memory. SC places the Dtag

state for block B in DtagTB, marks the buffer valid, and waits for the Writeback

transaction. If UltraSPARC

k

were also to victimize block A for block B, then block

B will simply overwrite block A in the Etags and the Dtags for UltraSPARC

k

. In

this case, the writeback buffer and DtagTB would not be used for this transaction,

since the line victim is clean.

7.6.3 Cache Coherence Sequence in Systems with Dtags

An example sequence of events:

1. UltraSPARC asserts its Req<n> signal to indicate that it wants to arbitrate

for the address bus. It eventually wins the arbitration and drives a request

packet on SYSADDR.

M–1

0

N

..

.

WB Buffer

A

A

B

System Controller

DtagTB k

DtagTB 1

0

Etag 1

Main Memory

Valid B

N–1

B

WB Buffer

X

0

Etag

k

N–1

A

N

Invalid

0

Dtag 1

N–1

A

...

0

Dtag

k

N–1

A

UltraSPARC

1

UltraSPARC

k

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...