Sun Microelectronics

120

UltraSPARC User’s Manual

S_REPLY takes a single interconnect clock cycle. SC asserts S_REPLY to initiate

data transfer to/from UltraSPARC and to acknowledge P_REQs from

UltraSPARC. Table 7-19 specifies the S_REPLY encodings.

SC must obey the following rules when generating S_REPLYs:

1. There is no ordering of S_REPLYs between transaction classes. Within each

Class, however, S_REPLYs must be strongly ordered.

2. Figure 7-24 on page 123 and Figure 7-25 on page 123 show S_REPLY timing

to the source and sink of data. UltraSPARC drives data 2 clock cycles after

receiving S_WAB, S_WAS, S_SRS or S_CRAB. UltraSPARC receives data 1

clock cycle after S_RBU, S_RBS, S_RAS, or S_SWIB.

3. Figure 7-26 on page 123 shows S_REPLY read data timing after receiving a

P_REPLY from UltraSPARC. There are a minimum of two clock cycles

between when SC receives the P_REPLY and when it can send the

S_REPLY to initiate the data transfer. Figure 7-26 also shows the handshake

for delivering data to UltraSPARC.

4. Figure 7-27 on page 124 shows the timing for back-to-back S_REQs for

Copyback. The earliest that SC can send another S_REQ to the same

UltraSPARC is the cycle after it sends the S_REPLY.

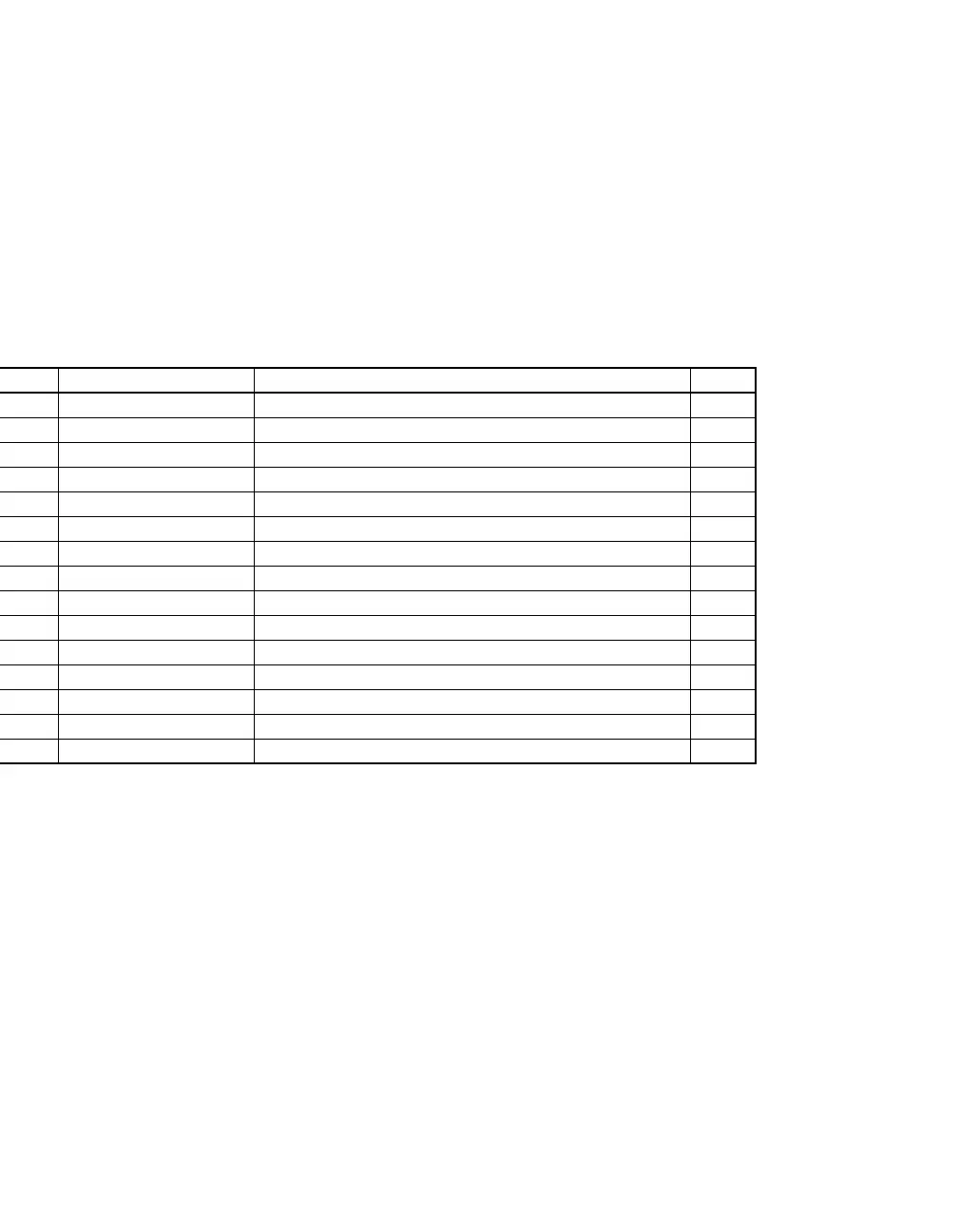

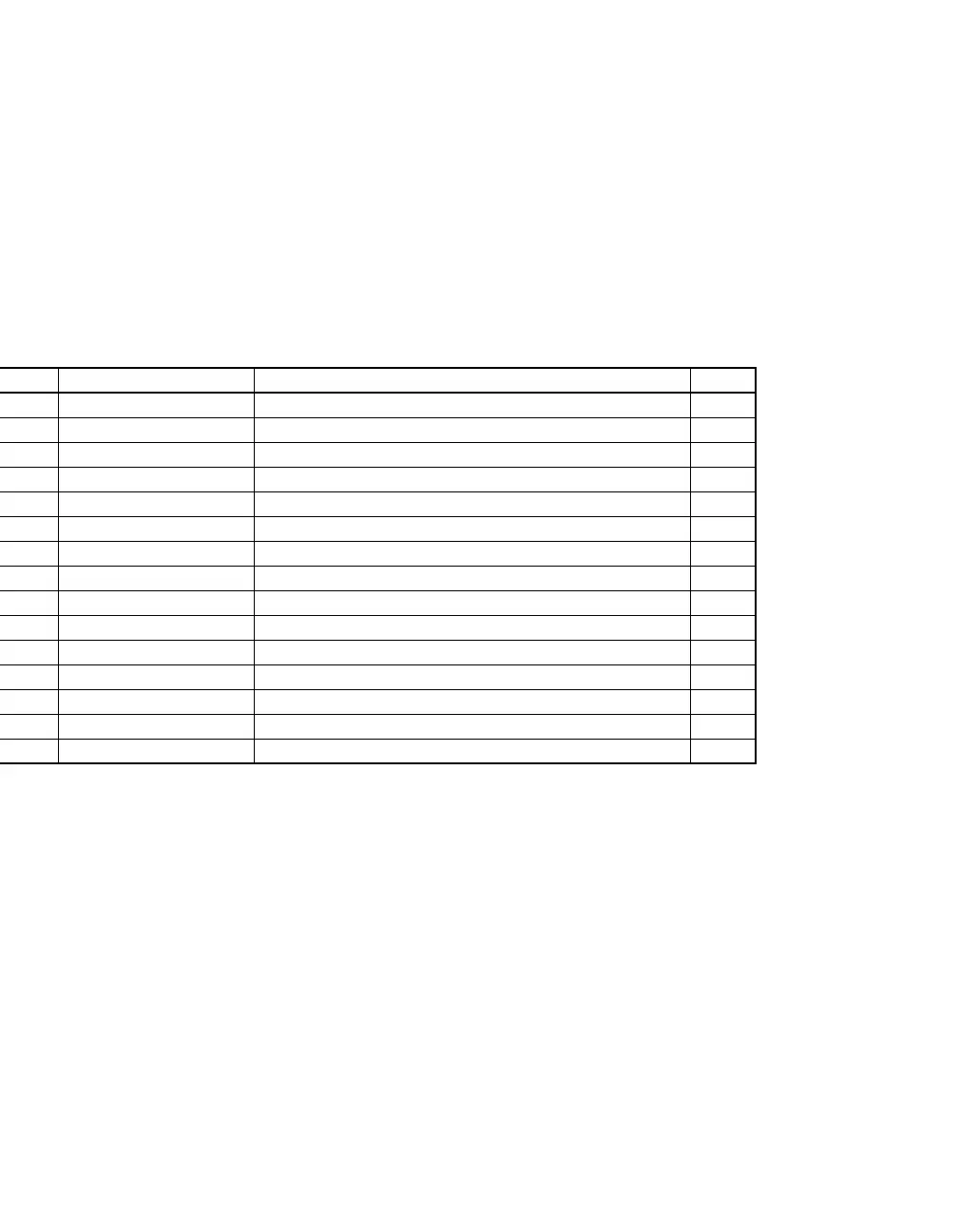

Table 7-19 S_REPLY Encoding

S_REPLY Name Reply to Transaction Type

S_IDLE Idle Default State 0000

S_ERR Error Report Read Error 0001

S_CRAB Coherent Read ACK Block To slave for P_SACK or P_SACKD reply 0010

S_WBCAN Writeback Cancel To master for P_WRB_REQ 0011

S_WAS Write ACK Single To master for P_NCWR_REQ 0100

S_WAB Write ACK Block To master for any block write 0101

S_OAK Ownership ACK To master for P_RDO_REQ 0110

S_INAK Interrupt NACK To master for P_INT_REQ 0111

S_RBU Read Block ACK Unshared To master for any block read 1000

S_RBS Read Block ACK Shared To master for coherent shared read 1001

S_RAS Read ACK Single To master for P_NCRD_REQ 1010

S_RTO Read Time Out To master, forwarding P_RTO, read to unimplemented address 1011

S_SRS Slave Read Single Read 16 bytes of data from slave 1110

S_SWIB Slave Write Interrupt Block Write 64 bytes of interrupt data to slave 1101

Reserved — — 1111

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...