Sun Microelectronics

148

UltraSPARC User’s Manual

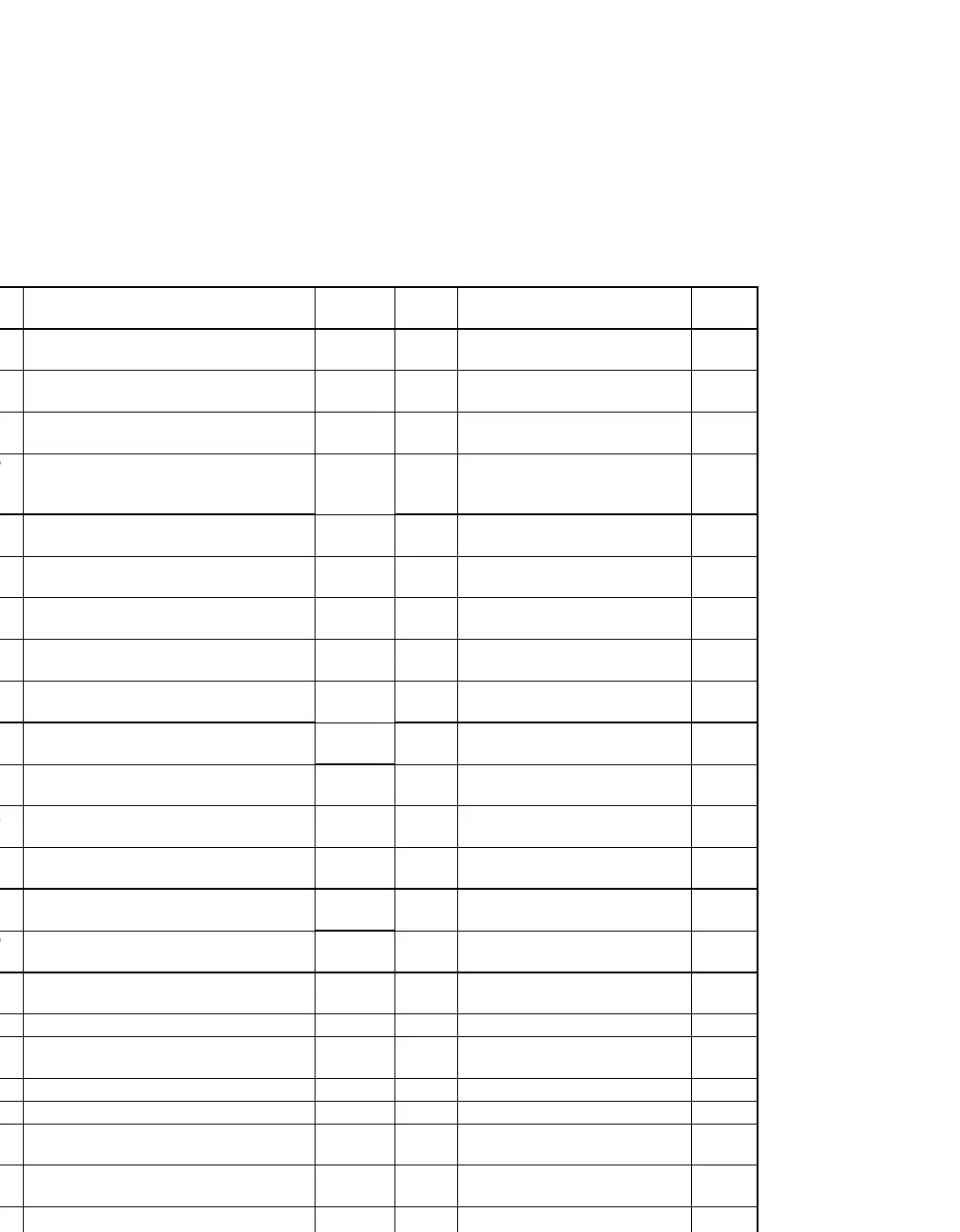

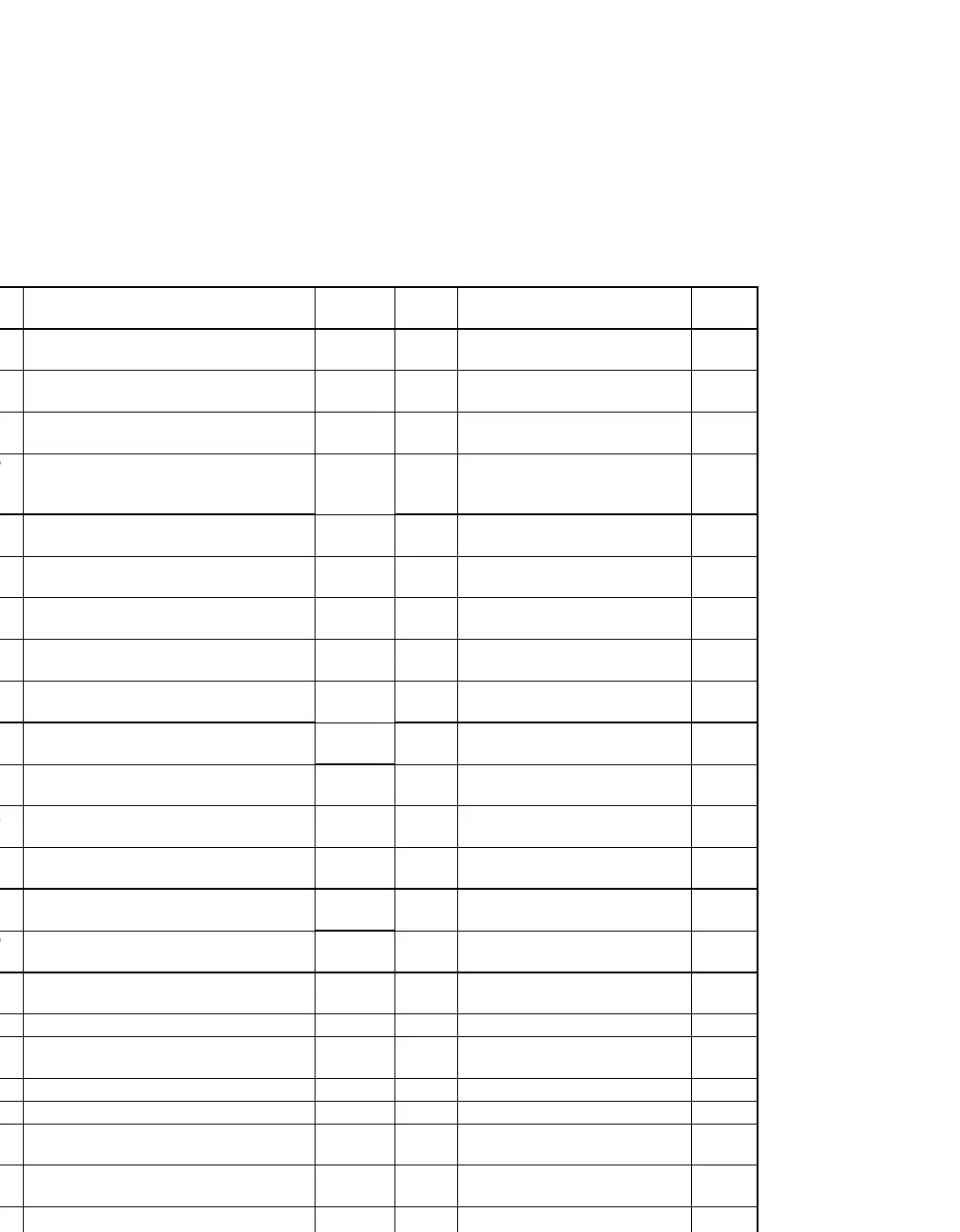

Table 8-2 UltraSPARC Extended (non-SPARC-V9) ASIs

ASI

Value

ASI Name (Suggested Macro Syntax) VA Access Description Section

14

16

ASI_PHYS_USE_EC

(ASI_PHYS_USE_EC)

—RW

2,5

Physical address, external cache-

able only

6.10

15

16

ASI_PHYS_BYPASS_EC_WITH_EBIT

(ASI_PHYS_BYPASS_EC_WITH_EBIT)

—RW

2

Physical address, non-cacheable,

with side-effect

6.10

1C

16

ASI_PHYS_USE_EC_LITTLE

(ASI_PHYS_USE_EC_L)

—RW

2,5

Physical address, external cache-

able only, little endian

6.10

1D

16

ASI_PHYS_BYPASS_EC_WITH_EBIT_LI

TTLE

(ASI_PHYS_BYPASS_EC_WITH_EBIT_L)

—RW

2

Physical address, non-cacheable,

with side-effect, little endian

6.10

24

16

ASI_NUCLEUS_QUAD_LDD

(ASI_NUCLEUS_QUAD_LDD)

—R

1,3

Cacheable, 128-bit atomic LDDA 13.6.3

2C

16

ASI_NUCLEUS_QUAD_LDD_LITTLE

(ASI_NUCLEUS_QUAD_LDD_L)

—R

1,3

Cacheable, 128-bit atomic LDDA,

little endian

13.6.3

45

16

ASI_LSU_CONTROL_REG

(ASI_LSU_CONTROL_REG)

0

16

RW Load/store unit control register A.6

46

16

ASI_DCACHE_DATA

(ASI_DCACHE_DATA)

— RW D-Cache data RAM diagnostics

access

A.8.1

47

16

ASI_DCACHE_TAG

(ASI_DCACHE_TAG)

— RW D-Cache tag/valid RAM diag-

nostics access

A.8.2

48

16

ASI_INTR_DISPATCH_STATUS

(ASI_INTR_DISPATCH_STATUS)

0

16

R

1

Interrupt vector dispatch status 9.3.3

49

16

ASI_INTR_RECEIVE

(ASI_INTR_RECEIVE)

0

16

RW Interrupt vector receive status 9.3.5

4A

16

ASI_UPA_CONFIG_REG

(ASI_UPA_CONFIG_REG)

0

16

RW UPA configuration register 8.3.3.2

4B

16

ASI_ESTATE_ERROR_EN_REG

(ASI_ESTATE_ERROR_EN_REG)

0

16

RW E-Cache error enable register 11.3.1

4C

16

ASI_AFSR (ASI_AFSR) 0

16

RW Asynchronous fault status regis-

ter

11.3.3

4D

16

ASI_AFAR (ASI_AFAR) 0

16

RW Asynchronous fault address reg-

ister

11.3.2

4E

16

ASI_ECACHE_TAG_DATA

(ASI_EC_TAG_DATA)

0

16

RW E-Cache tag/valid RAM data

diagnostic access

A.9.2

50

16

ASI_IMMU (ASI_IMMU) 0

16

R

1

I-MMU Tag Target Register 6.9.2

50

16

ASI_IMMU (ASI_IMMU) 18

16

RW I-MMU Synchronous Fault Status

Register

6.9.4

50

16

ASI_IMMU (ASI_IMMU) 28

16

RW I-MMU TSB Register 6.9.5.1

50

16

ASI_IMMU (ASI_IMMU) 30

16

RW I-MMU TLB Tag Access Register 6.9.7

51

16

ASI_IMMU_TSB_8KB_PTR_REG

(ASI_IMMU_TSB_8KB_PTR_REG)

0

16

R

1

I-MMU TSB 8KB Pointer Register 6.9.8

52

16

ASI_IMMU_TSB_64KB_PTR_REG

(ASI_IMMU_TSB_64KB_PTR_REG)

0

16

R

1

I-MMU TSB 64KB Pointer Regis-

ter

6.9.8

54

16

ASI_ITLB_DATA_IN_REG

(ASI_ITLB_DATA_IN_REG)

0

16

W

1

I-MMU TLB Data In Register 6.9.9

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...