Sun Microelectronics

164

UltraSPARC User’s Manual

9.3.1 Outgoing Interrupt Vector Data<2:0>

Name: Outgoing Interrupt Vector Data Registers (Privileged)

ASI_UDB_INTR_W (data 0): ASI=77

16

, VA<63:0>=40

16

ASI_UDB_INTR_W (data 1): ASI=77

16

, VA<63:0>=50

16

ASI_UDB_INTR_W (data 2): ASI=77

16

, VA<63:0>=60

16

Data: Interrupt data.

A write to these registers modifies the out-going interrupt dispatch data registers.

Non-privileged access to this register causes a

privileged_action

trap.

9.3.2 Interrupt Vector Dispatch

Name: ASI_UDB_INTR_W (interrupt dispatch) (Privileged, write-only)

ASI: 77

16

, VA<63:19>=0, VA<18:14>= target MID, VA<13:0>=70

16

A write to this ASI triggers an interrupt vector dispatch to the target CPU resid-

ing at slot MID (Module ID) along with the contents of the three Interrupt Vector

Data Registers.

A read from this ASI causes a

data_access_exception

trap.

Non-privileged access to this register causes a

privileged_action

trap.

9.3.3 Interrupt Vector Dispatch Status Register

Name: ASI_INTR_DISPATCH_STATUS (Privileged, read-only)

ASI: 48

16

, VA<63:0>=0

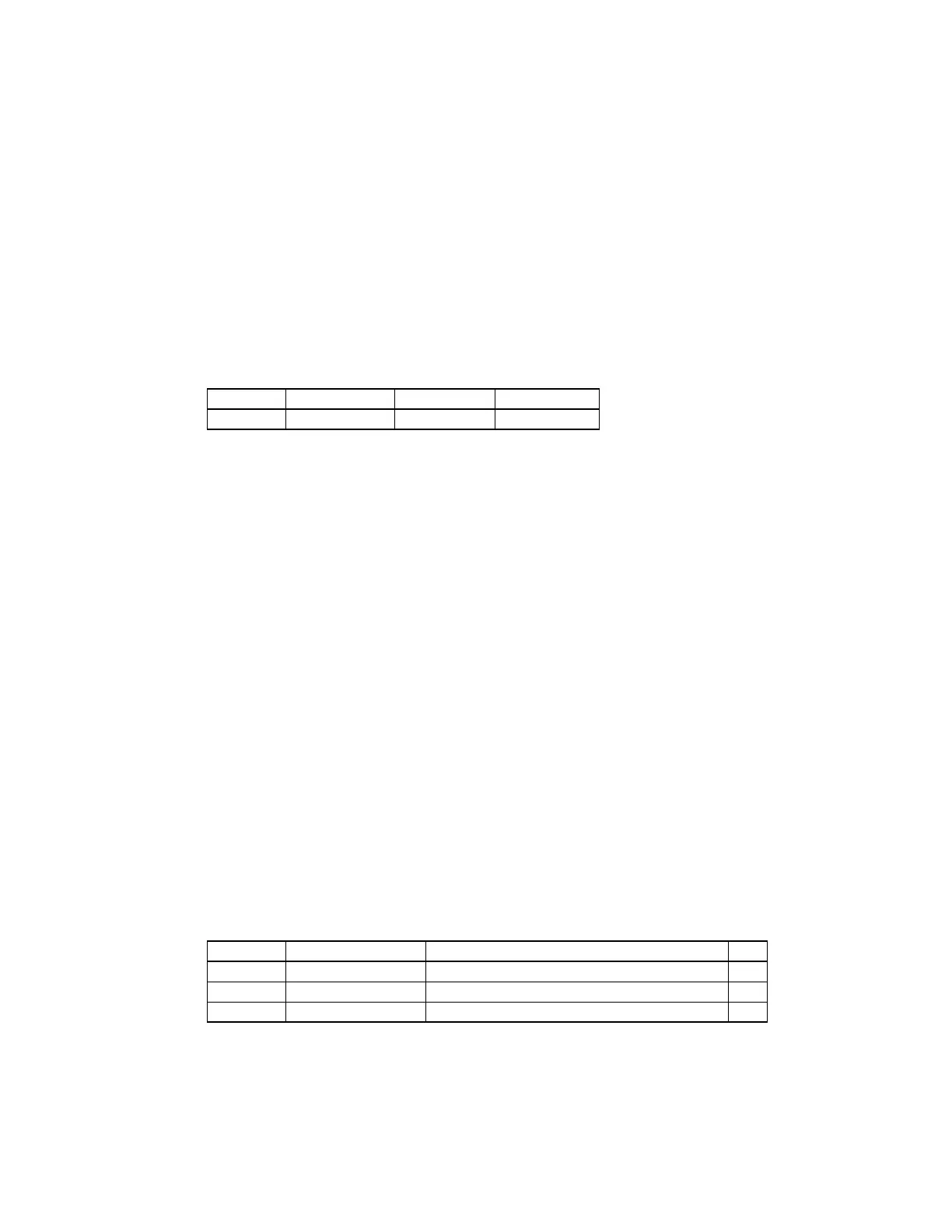

Table 9-1 Outgoing Interrupt Vector Data Register Format

Bits Field Use RW

<63:0> Data Data W

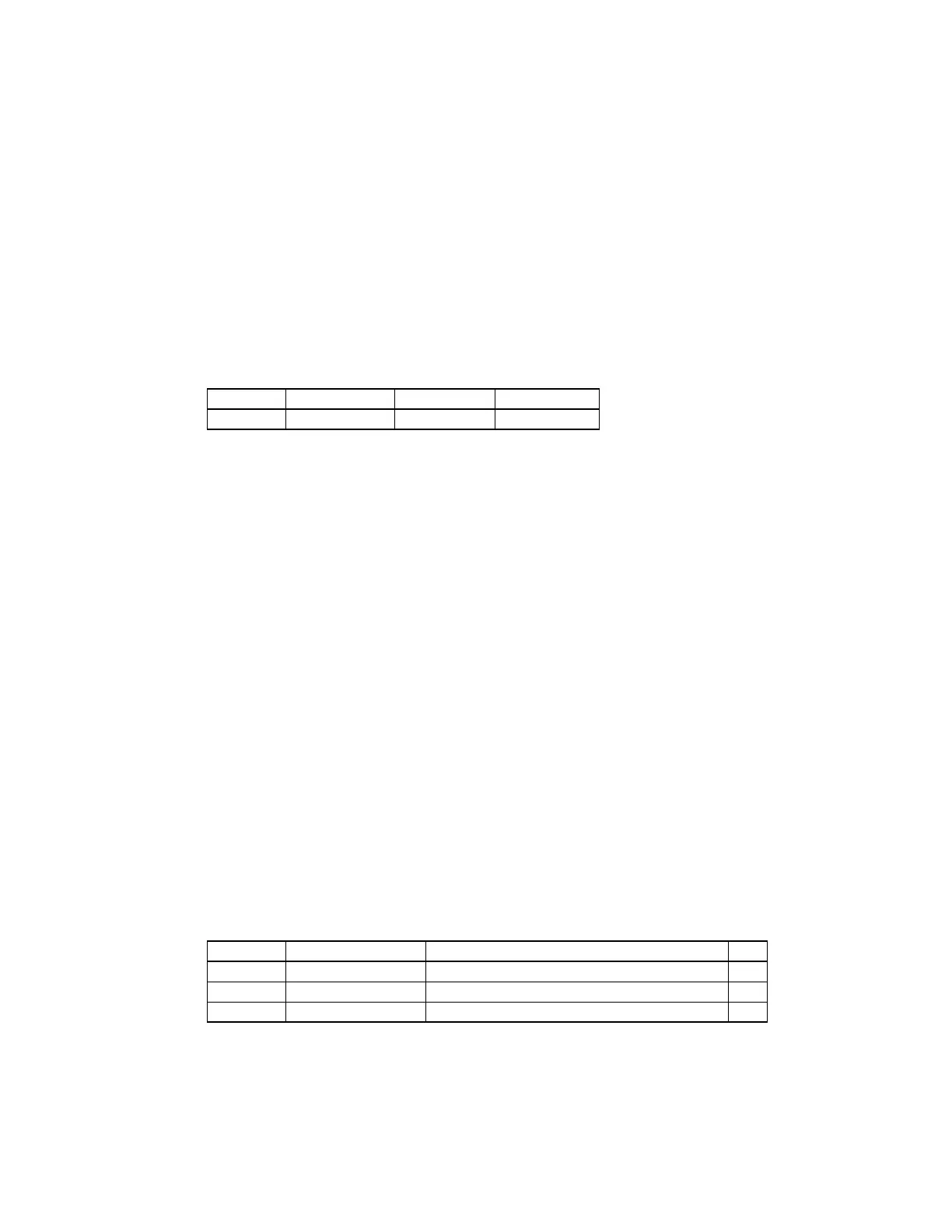

Table 9-2 Interrupt Dispatch Status Register Format

Bits Field Use RW

<63:2> Reserved —R

<1> NACK Set if interrupt dispatch has failed R

<0> BUSY Set when there is an outstanding dispatch R

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...