Sun Microelectronics

7

1. UltraSPARC Basics

1.3.3 Integer Execution Unit (IEU)

The IEU contains the following components:

• Two ALUs

• A multi-cycle integer multiplier

• A multi-cycle integer divider

• Eight register windows

• Four sets of global registers (normal, alternate, MMU, and interrupt globals)

• The trap registers (See Table 1-2 for supported trap levels)

1.3.4 Floating-Point Unit (FPU)

The FPU is partitioned into separate execution units, which allows the

UltraSPARC processor to issue and execute two floating-point instructions per

cycle. Source and result data are stored in the 32-entry register file, where each

entry can contain a 32-bit value or a 64-bit value. Most instructions are fully pipe-

lined, (with a throughput of one per cycle), have a latency of three, and are not

affected by the precision of the operands (same latency for single- or double-pre-

cision). The divide and square root instructions are not pipelined and take 12/22

cycles (single/double) to execute but they do not stall the processor. Other in-

structions, following the divide/square root can be issued, executed, and retired

to the register file before the divide/square root finishes. A precise exception

model is maintained by synchronizing the floating-point pipe with the integer

pipe and by predicting traps for long latency operations. See Section 7.3.1, “Pre-

cise Traps,” in The SPARC Architecture Manual, Version 9.

1.3.5 Graphics Unit (GRU)

UltraSPARC introduces a comprehensive set of graphics instructions that provide

fast hardware support for two-dimensional and three-dimensional image and

video processing, image compression, audio processing, etc. 16-bit and 32-bit par-

titioned add, boolean, and compare are provided. 8-bit and 16-bit partitioned

multiplies are supported. Single cycle pixel distance, data alignment, packing,

and merge operations are all supported in the GRU.

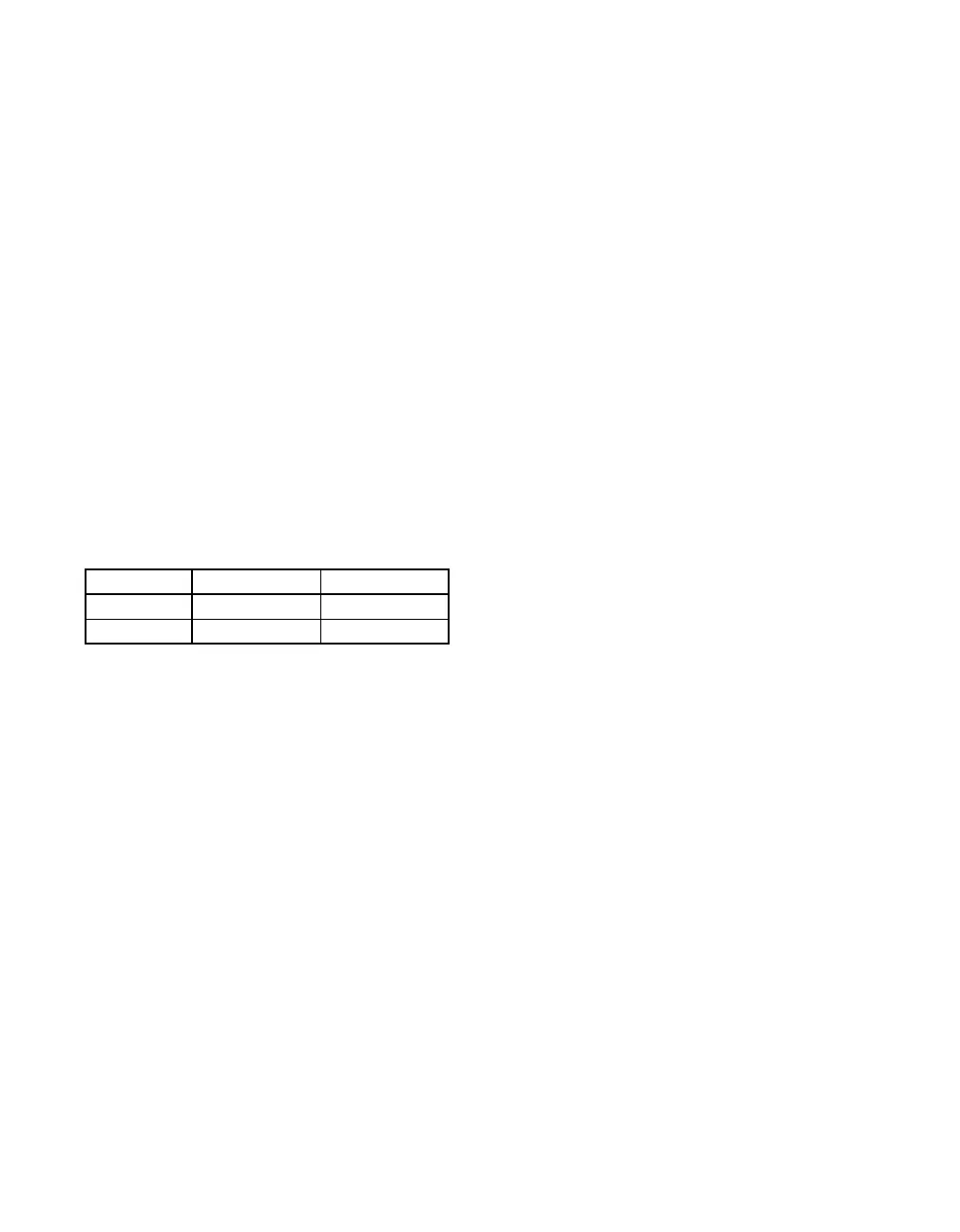

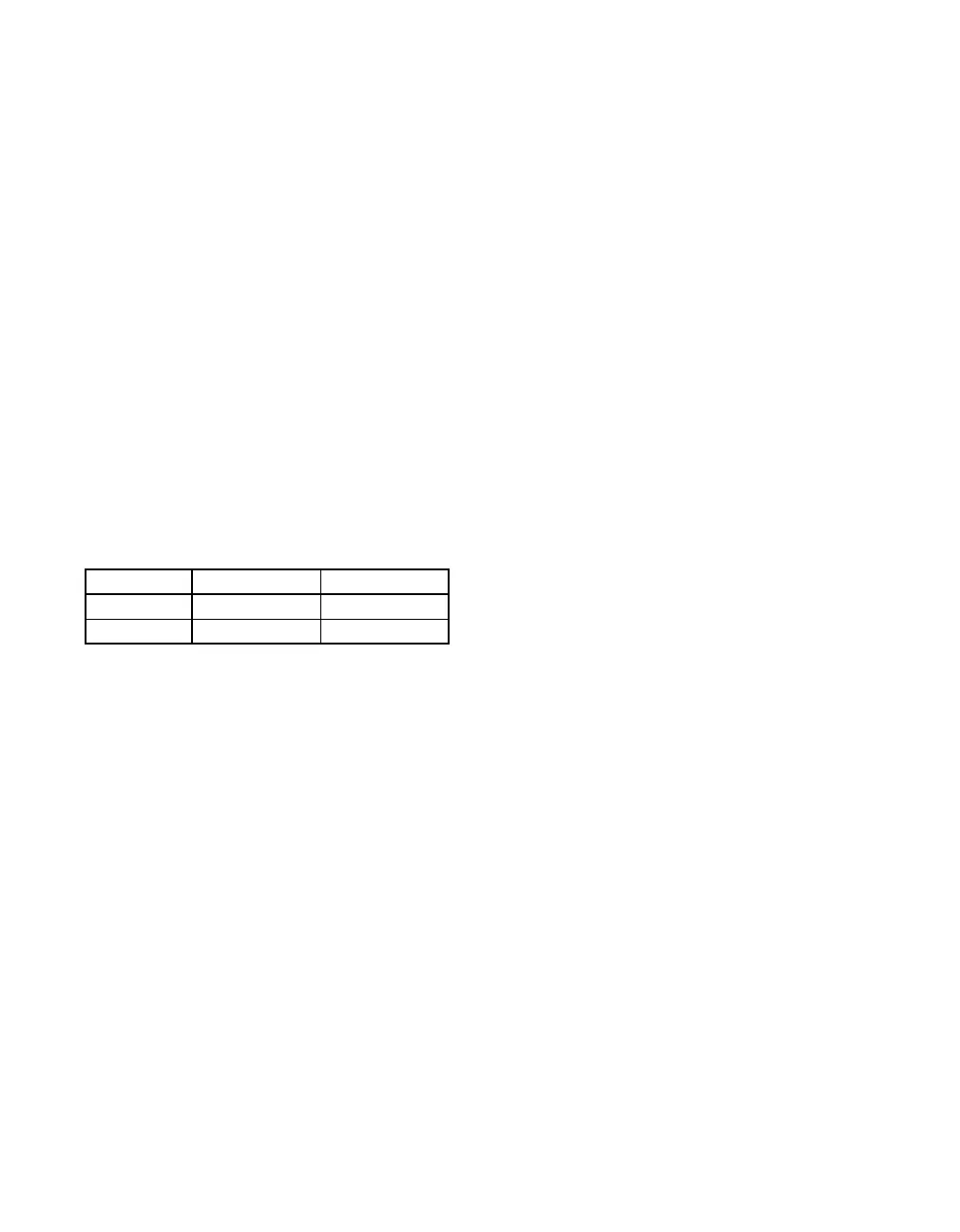

Table 1-2 Supported Trap Levels

UltraSPARC-I UltraSPARC-II

MAXTL 44

Trap Levels 55

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...