Sun Microelectronics

241

14. Implementation Dependencies

14.2.3 Integer Multiply and Divide

Integer multiplications (MULScc, SMUL{cc}, MULX) and divisions (SDIV{cc},

UDIV{cc}, UDIVX) are executed directly in hardware.

Multiplications are done 2 bits at a time with early exit when the final result is

generated. Divisions use a 1-bit non-restoring division algorithm.

Note: For best performance, the smaller of the two operands of a multiply

should be the rs1 operand.

14.2.4 Version Register (Impdep #2, 13, 101, 104)

Consult the product data sheet for the content of the Version Register for an im-

plementation. For the state of this register after resets, see Table 10-1, “Machine

State After Reset and in RED_state,” on page 172.

manuf: 16-bit manufacturer code, 0017

16

(TI JEDEC number), that identifies the

manufacturer of an UltraSPARC CPU.

impl: 16-bit implementation code, 0010

16

, that uniquely identifies an

UltraSPARC-class CPU. Table 14-3 shows the VER.impl values for each

UltraSPARC model.

mask: 8-bit mask set revision number that identifies the mask set revision of this

UltraSPARC. This is subdivided into a 4 bit major mask number <31:28>

and a 4-bit minor mask number <27:24>. The major number starts at zero

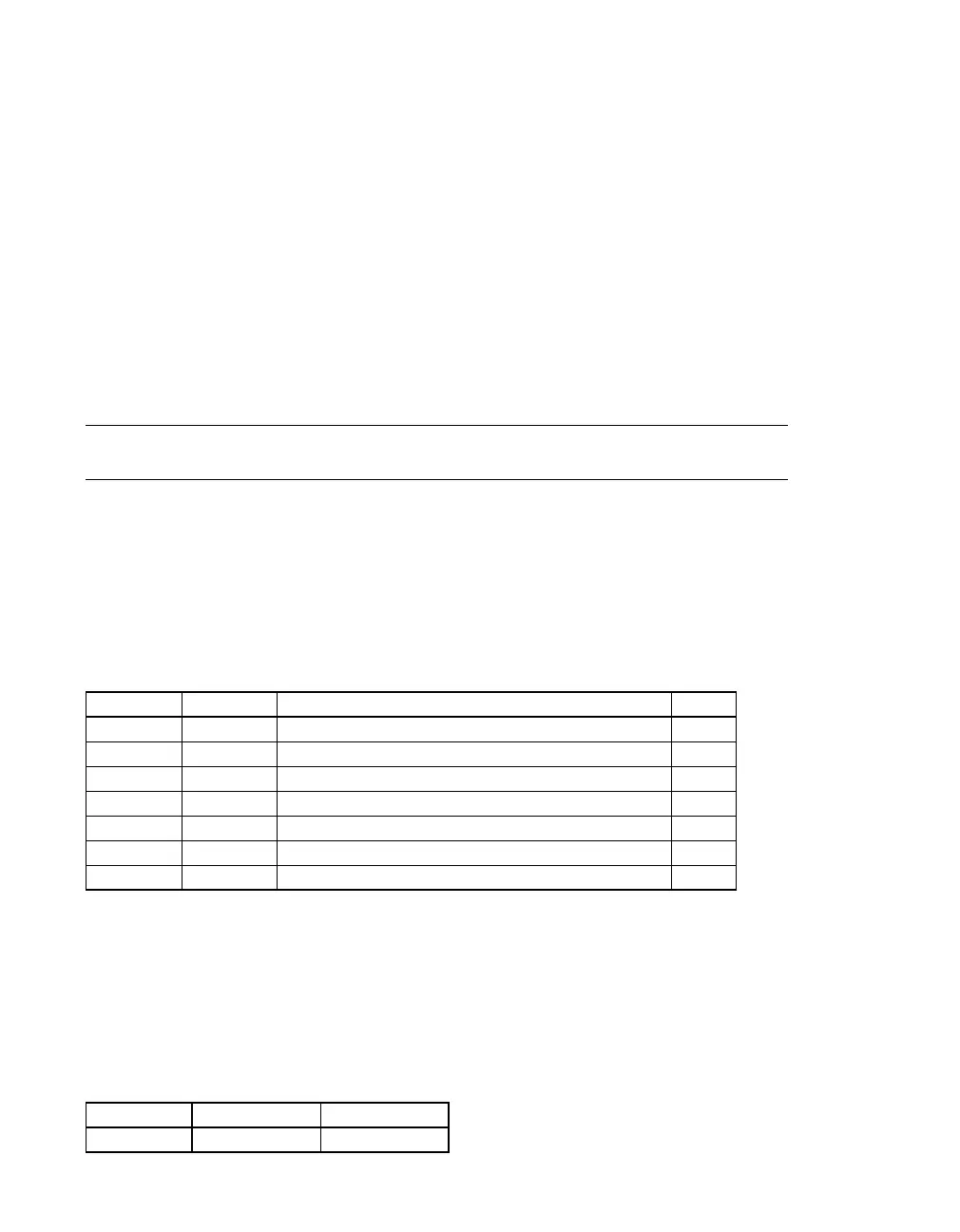

Table 14-2 Version Register Format

Bits Field Use RW

<63:48> manuf Manufacturer identification R

<47:32> impl Implementation identification R

<31:24> mask Mask set version R

<23:16> Reserved —R

<15:8> maxtl Maximum trap level supported R

<7:5> Reserved —R

<4:0> maxwin Maximum number of windows of integer register file. R

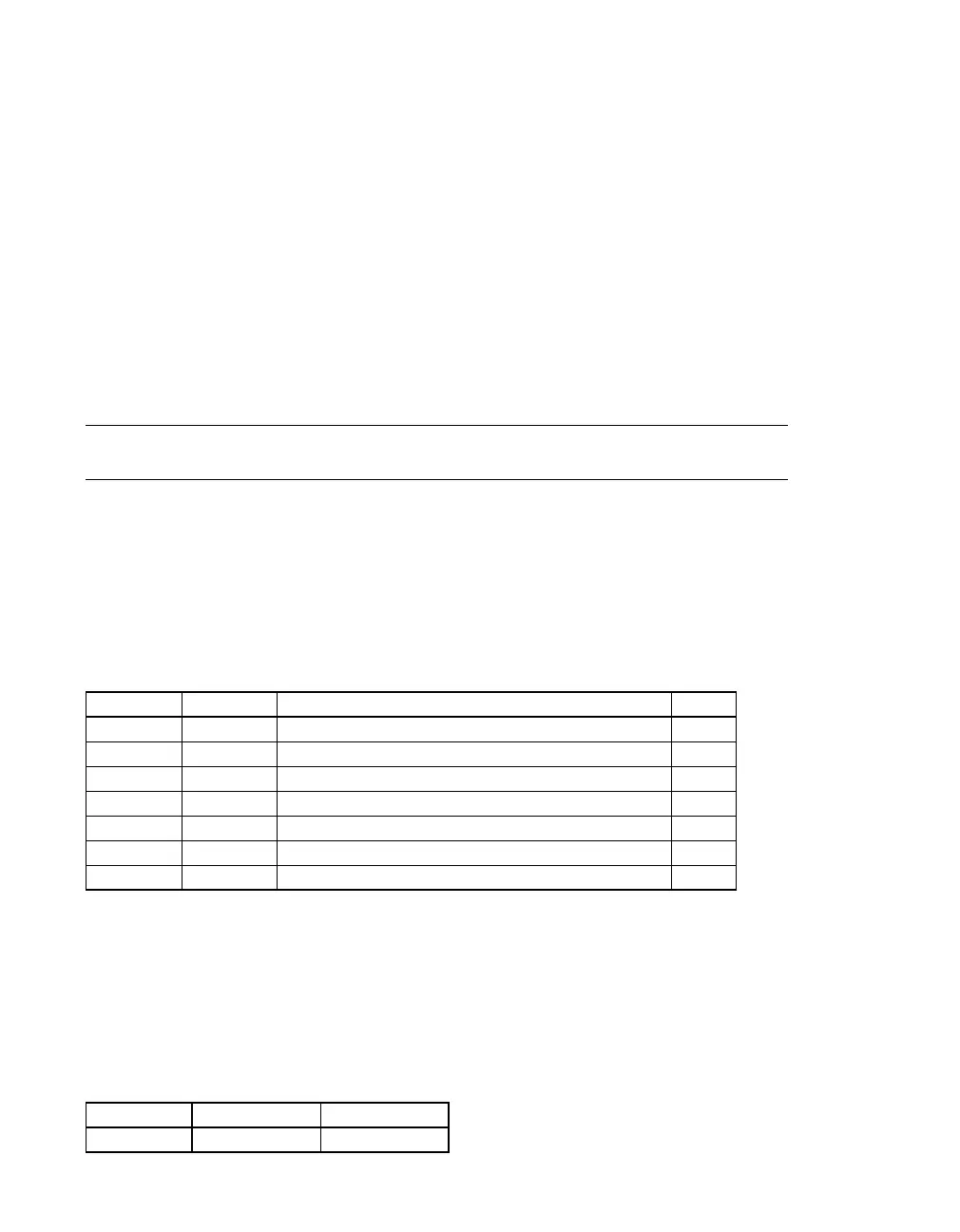

Table 14-3 VER.impl Values by UltraSPARC Model

UltraSPARC-I UltraSPARC-II

VER.impl 0010

16

0011

16

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...