Sun Microelectronics

248

UltraSPARC User’s Manual

FLUSH effective address is translated by the D-MMU. As a result, FLUSH can

cause a

data_access_exception

(the page is mapped with side effects or no fault

only bits set, virtual address out of range, or privilege violation) or a

data_access_MMU_miss

trap. For a

data_access_exception

, the trap handler can de-

code the FLUSH instruction, and perform a Done to be consistent with the nor-

mal SPARC-V9 behavior of no traps on FLUSH. For a

data_access_MMU_miss

, the

trap handler should do the normal TLB miss processing and perform a RETRY if

the page can be mapped in the TLB, otherwise perform a DONE.

Note: SPARC-V9 specifies that the FLUSH instruction has no latency on the

issuing processor. In other words, a store to instruction space prior to the FLUSH

instruction is visible immediately after the completion of FLUSH. MEMBAR

#StoreStore is required to ensure proper ordering in multi-processing system

when the memory model is not TSO. When a MEMBAR #StoreStore, FLUSH

sequence is performed, UltraSPARC guarantees that earlier code modifications

will be visible across the whole system.

14.4.5 PREFETCH{A} (Impdep #103, 117)

For UltraSPARC-I, PREFETCH{A} instructions with fcn=0..4 are treated as NOPs.

For UltraSPARC-II, PREFETCH{A} instructions with fcn=0..4 have the following

meanings:

PREFETCH{A} instructions with fcn=5..15 cause an

illegal_instruction

trap.

PREFETCH{A} instructions with fcn=16..31 are treated as NOPs.

14.4.6 Non-faulting Load and MMU Disable (Impdep #117)

When the data MMU is disabled, accesses are assumed to be non-cacheable

(TTE.PC=0) and with side-effect (TTE.E=1). Non-faulting loads encountered

when the MMU is disabled cause a

data_access_exception

trap with SFSR.FT=2

(speculative load to page with side-effect attribute).

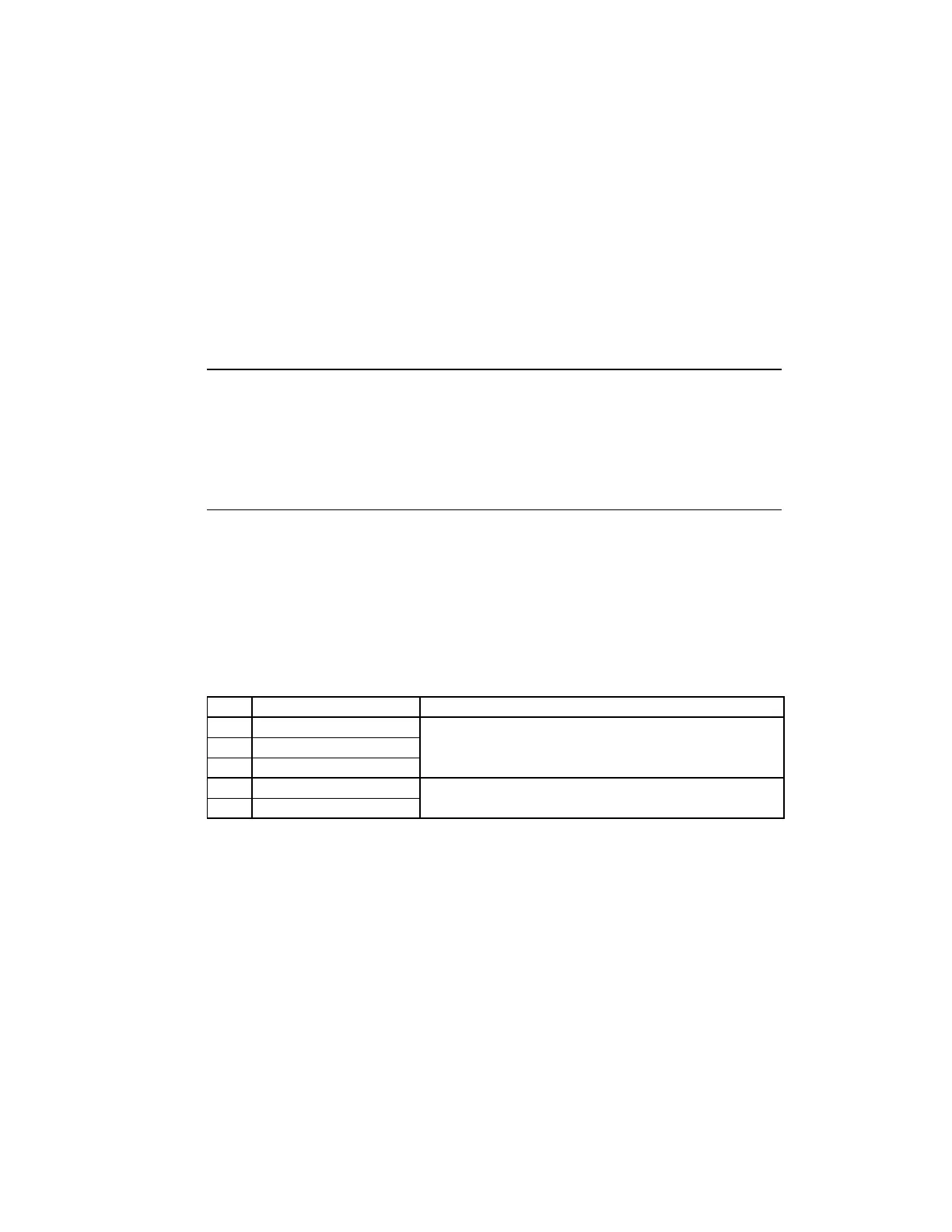

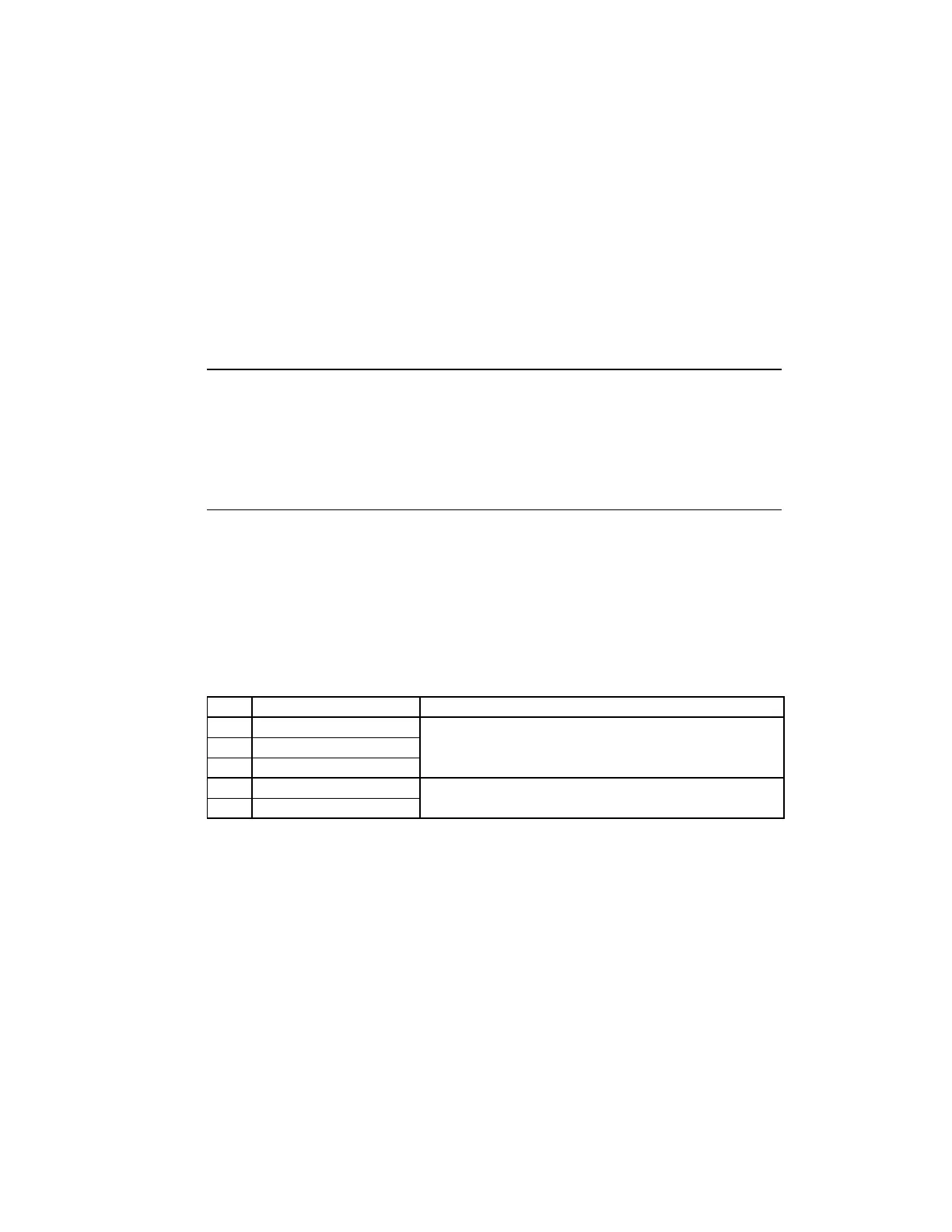

Table 14-10 PREFETCH{A} Variants (UltraSPARC-II)

fcn Prefetch Function Action

0 Prefetch for several reads

Generate P_RDS_REQ if desired line is not present in E-Cache1 Prefetch for one read

2 Prefetch page

3 Prefetch for several writes

Generate P_RDO_REQ if desired line is not present in E-Cache in

either E or M state

4 Prefetch for one write

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...