Sun Microelectronics

310

UltraSPARC User’s Manual

Note: To simplify the implementation, read access to the instruction cache fields

(ASIs 60

16

.. 6F

16

) must use the LDDA instruction instead of LDXA or LDDFA.

Using another type of load causes a

data_access_exception

trap (with SFSR.FT=8,

Illegal ASI size). LDDA will update two registers. The useful data is in the odd

register, the contents of the even register are undefined.

A.7.1 I-Cache Instruction Fields

ASI 66

16

, VA<63:14>=0, VA<13>=IC_set, VA<12:3>=IC_addr, VA<2:0>=0

Name: ASI_ICACHE_INSTR

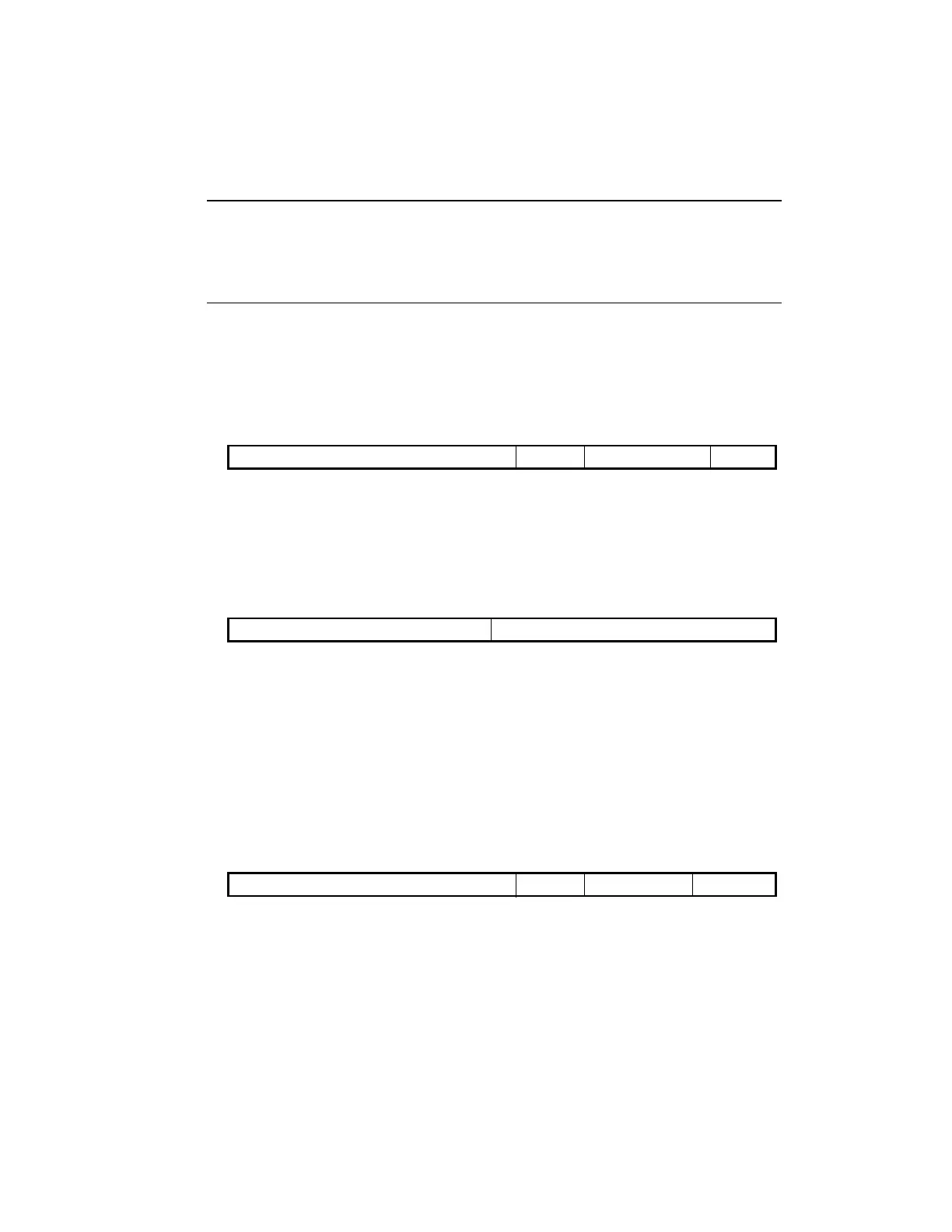

Figure A-6 I-Cache Instruction Access Address Format (ASI 66

16

)

IC_set: This 1-bit field selects a set (2-way associative).

IC_addr: This 10-bit index <12:3> selects an aligned pair of 32-bit instructions.

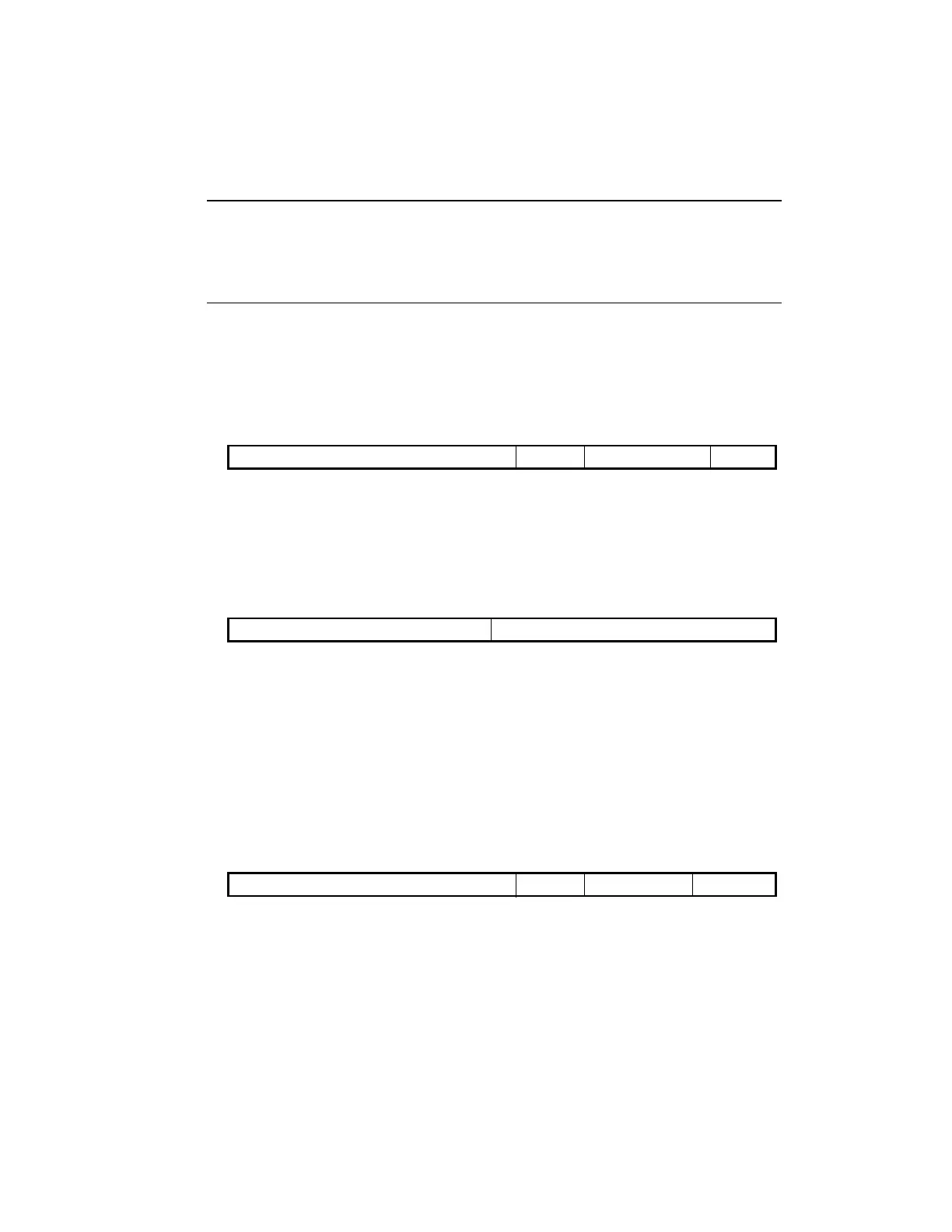

Figure A-7 I-Cache Instruction Access Data Format (ASI 66

16

)

IC_instr: Two 32-bit instruction fields

A.7.2 I-Cache Tag/Valid Fields

ASI 67

16

, VA<63:14>=0, VA<13>=IC_set, VA<12:5>=IC_addr, VA<4:0>=0

Name: ASI_ICACHE_TAG

Figure A-8 I-Cache Tag/Valid Access Address Format (ASI 67

16

)

IC_set: This 1-bit field selects a set (2-way associative).

IC_addr: This 8-bit index (VA<12:5>) selects a cache tag.

63 230

— —

IC_set

IC_addr

121314

63 0

IC_instr 0

3233

IC_instr 1

63 450

— —

IC_set

IC_addr

121314

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...