Sun Microelectronics

43

6. MMU Internal Architecture

Soft<5:0>, Soft2<8:0>: Software-defined fields, provided for use by the operating

system. The Soft and Soft2 fields may be written with any value; they

read as zero.

Diag: Used by diagnostics to access the redundant information held in the TLB

structure. Diag<0>=Used bit, Diag<3:1>=RAM size bits, Diag<6:4>=CAM

size bits. (Size bits are 3-bit encoded as 000=8K, 001=64K, 011=512K,

111=4M.) The size bits are read-only; the Used bit is read/write. All other

Diag bits are reserved.

PA<40:13>: The physical page number. Page offset bits for larger page sizes

(PA<15:13>, PA<18:13>, and PA<21:13> for 64Kb, 512Kb, and 4Mb pages,

respectively) are stored in the TLB and returned for a Data Access read,

but ignored during normal translation.

L: Lock. If this bit is set, the TTE entry will be “locked down” when it is

loaded into the TLB; that is, if this entry is valid, it will not be replaced by

the automatic replacement algorithm invoked by an ASI store to the Data

In register. The lock bit has no meaning for an invalid entry. Arbitrary

entries may be locked down in the TLB. Software must ensure that at

least one entry is not locked when replacing a TLB entry, otherwise the

last TLB entry will be replaced.

CP, CV: The cacheable-in-physically-indexed-cache and cacheable-in-virtually-

indexed-cache bits determine the placement of data in UltraSPARC

caches, according to Table 6-2. The MMU does not operate on the

cacheable bits, but merely passes them through to the cache subsystem.

The CV-bit in the I-MMU is read as zero and ignored when written.

E: Side-effect. If this bit is set, speculative loads and FLUSHes will trap for

addresses within the page, noncacheable memory accesses other than

block loads and stores are strongly ordered against other E-bit accesses,

and noncacheable stores are not merged. This bit should be set for pages

that map I/O devices having side-effects. Note, however, that the E-bit

does not prevent normal instruction prefetching. The E-bit in the I-MMU

is read as zero and ignored when written.

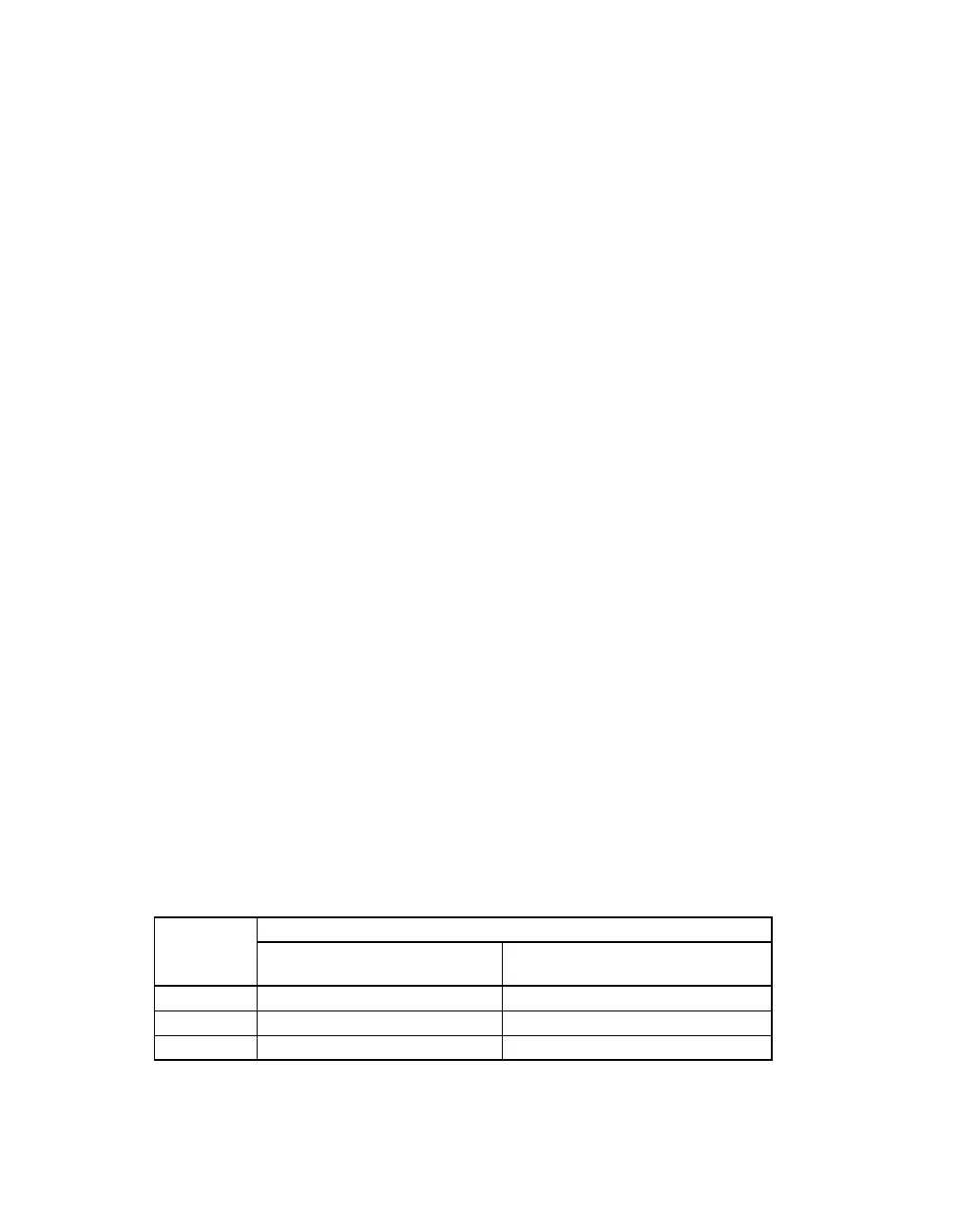

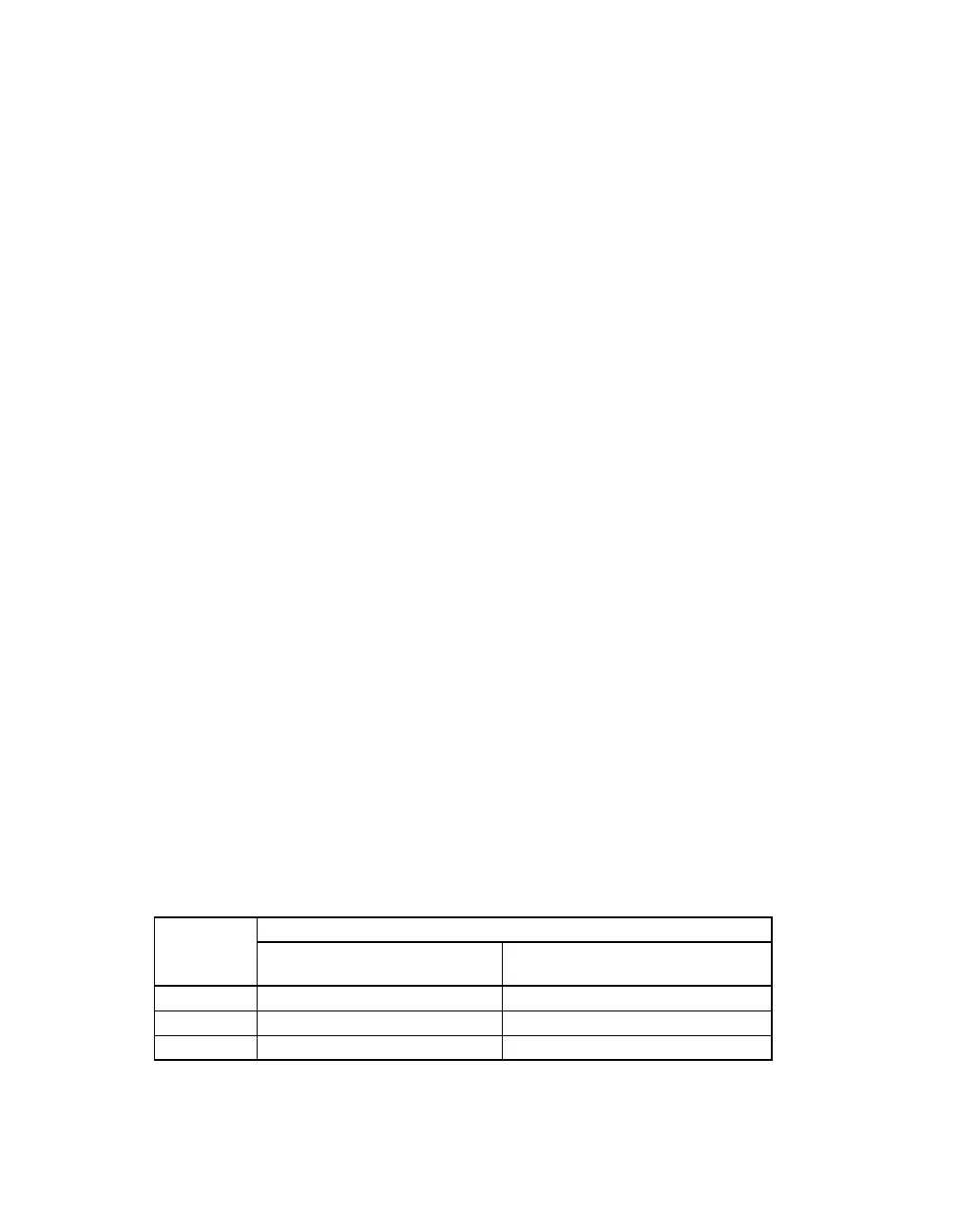

Table 6-2 Cacheable Field Encoding (from TSB)

Cacheable

{CP, CV}

Meaning of TTE When Placed in:

iTLB

(I-Cache PA-Indexed)

dTLB

(D-Cache VA-Indexed)

0x Non-cacheable Non-cacheable

10 Cacheable E-Cache, I-Cache Cacheable E-Cache only

11 Cacheable E-Cache, I-Cache Cacheable E-Cache, D-Cache

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...