Sun Microelectronics

51

6. MMU Internal Architecture

• Attempted access using a restricted ASI in non-privileged mode. The MMU

signals a

privileged_action

exception for this case.

• An atomic instruction (including 128-bit atomic load) issued to a memory

address marked uncacheable in a physical cache (that is, with CP=0),

including cases in which the D-MMU is disabled. The MMU signals a

data_access_exception

trap (FT=04

16

) for this case.

• A data access (including FLUSH) with an ASI other than

ASI_{PRIMARY,SECONDARY}_NO_FAULT{_LITTLE} to a page marked with

the NFO (no-fault-only) bit. The MMU signals a

data_access_exception

trap

(FT=10

16

) for this case.

• Virtual address out of range (including FLUSH) and PSTATE.AM is not set.

The MMU signals a

data_access_exception

trap (FT=20

16

) for this case.

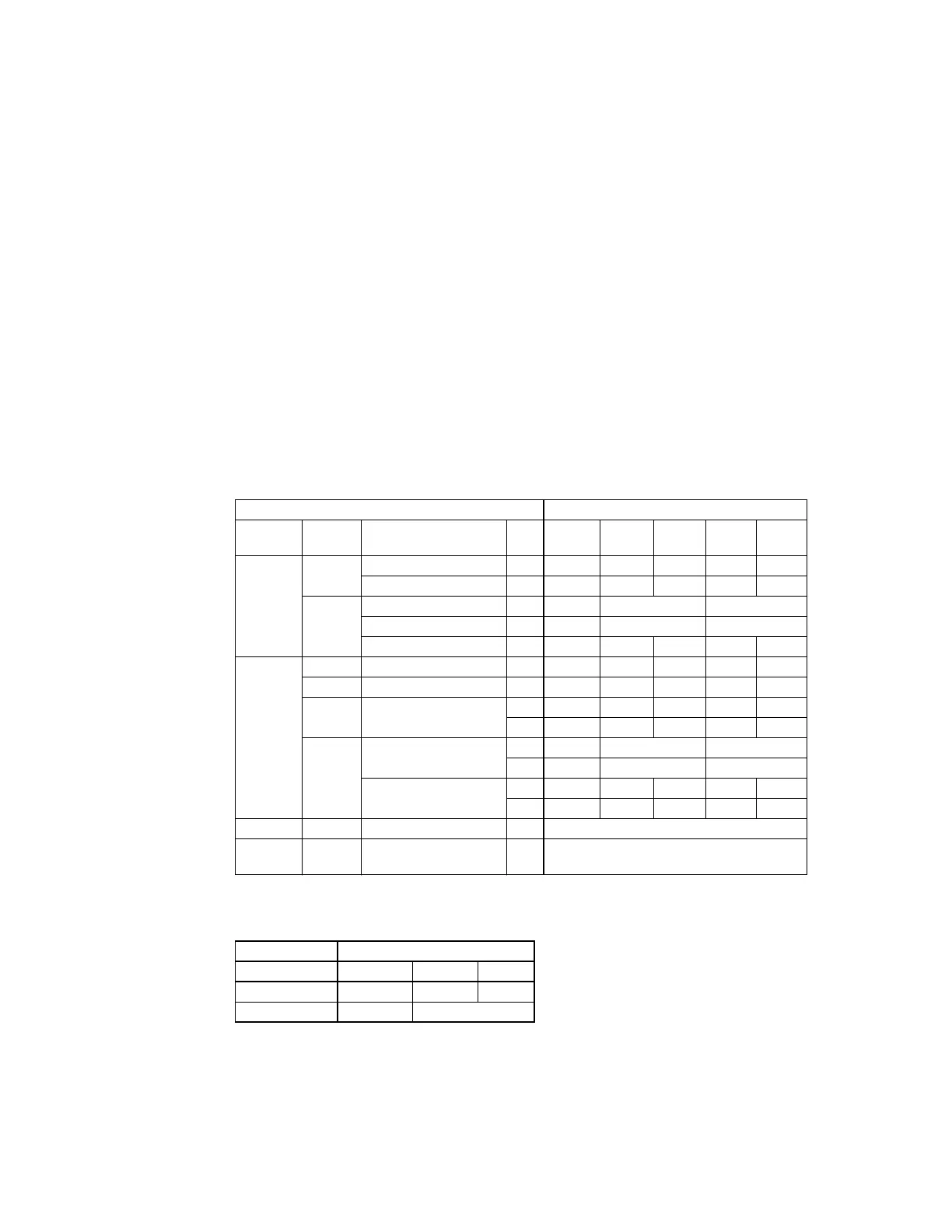

Table 6-4 D-MMU Operations for Normal ASIs

Condition Behavior

Opcode

PRIV

Mode

ASI W

TLB

Miss

E=0

P=0

E=0

P=1

E=1

P=0

E=1

P=1

Load

0 PRIM, SEC — DMISS OK DEXC OK DEXC

PRIM_NF, SEC_NF — DMISS OK DEXC DEXC DEXC

1 PRIM, SEC, NUC — DMISS OK OK

PRIM_NF, SEC_NF — DMISS OK DEXC

U_PRIM, U_SEC — DMISS OK DEXC OK DEXC

FLUSH

0—

DMISS OK DEXC DEXC DEXC

1—DMISS OK OK DEXC DEXC

Store or

Atomic

0 PRIM, SEC 0

DMISS DPROT DEXC DPROT DEXC

1 DMISS OK DEXC OK DEXC

1 PRIM, SEC, NUC 0 DMISS DPROT DPROT

1 DMISS OK OK

U_PRIM, U_SEC 0 DMISS DPROT DEXC DPROT DEXC

1 DMISS OK DEXC OK DEXC

— 0 BYPASS —

privileged_action

—

1 BYPASS — Bypass. No traps when D-MMU enabled,

PRIV=1.

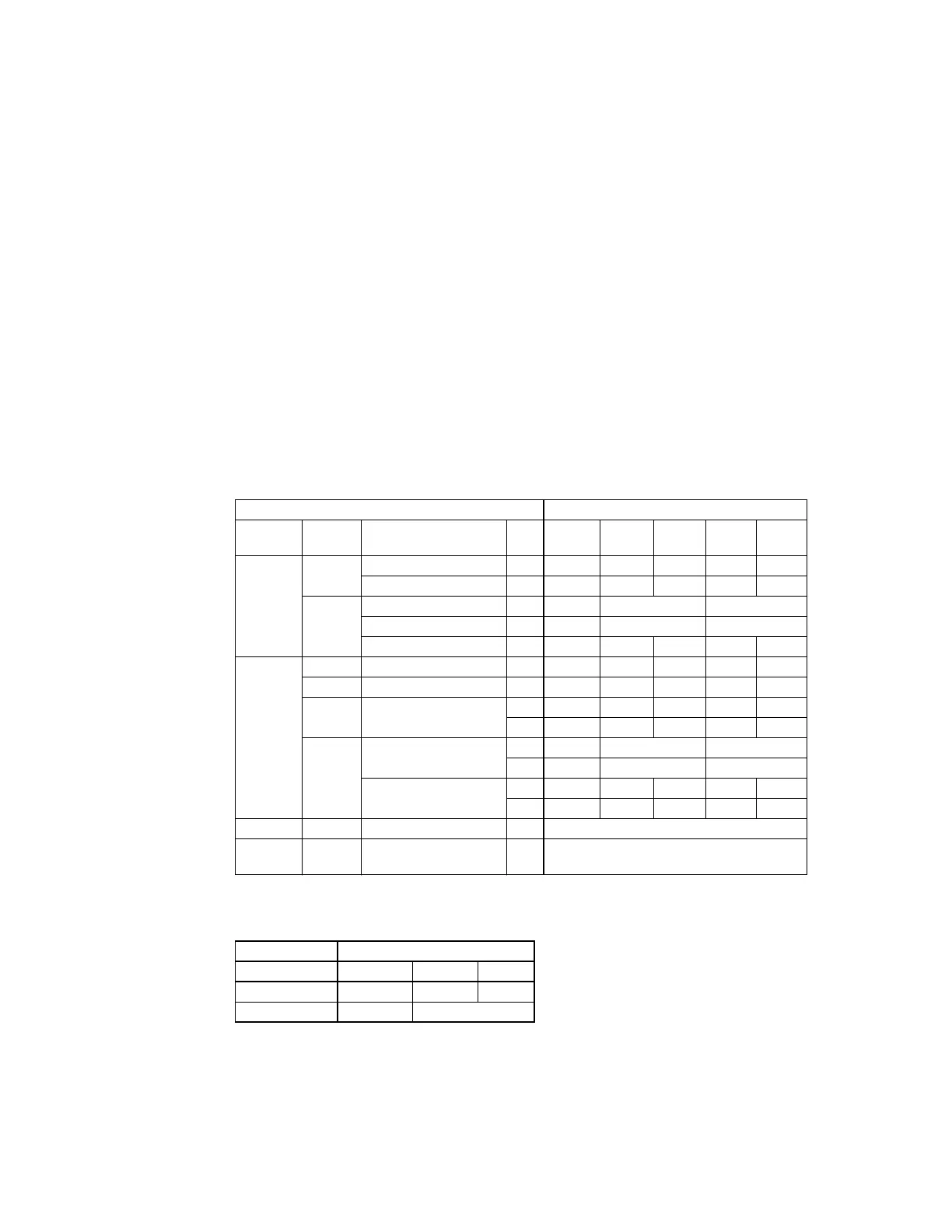

Table 6-5 I-MMU Operations for Normal ASIs

Condition Behavior

PRIV Mode TLB Miss P=0 P=1

0 IMISS OK IEXC

1 IMISS OK

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...