Sun Microelectronics

53

6. MMU Internal Architecture

1

Accesses to non-translating ASIs are always made in “big endian” mode, regardless of the setting of D-MMU.IE. See Section 8.3,

“Alternate Address Spaces,” on page 146 for information about non-translating ASIs.

The context register used by the data and instruction MMUs is determined from

the following table. A comprehensive list of ASI values can be found in the ASI

map in Section 8.3, “Alternate Address Spaces,” on page 146. The context register

selection is not affected by the endianness of the access.

a. Any ASI name containing the string “NUCLEUS”.

b. Any ASI name containing the string “PRIMARY”.

c. Any ASI name containing the string “SECONDARY”.

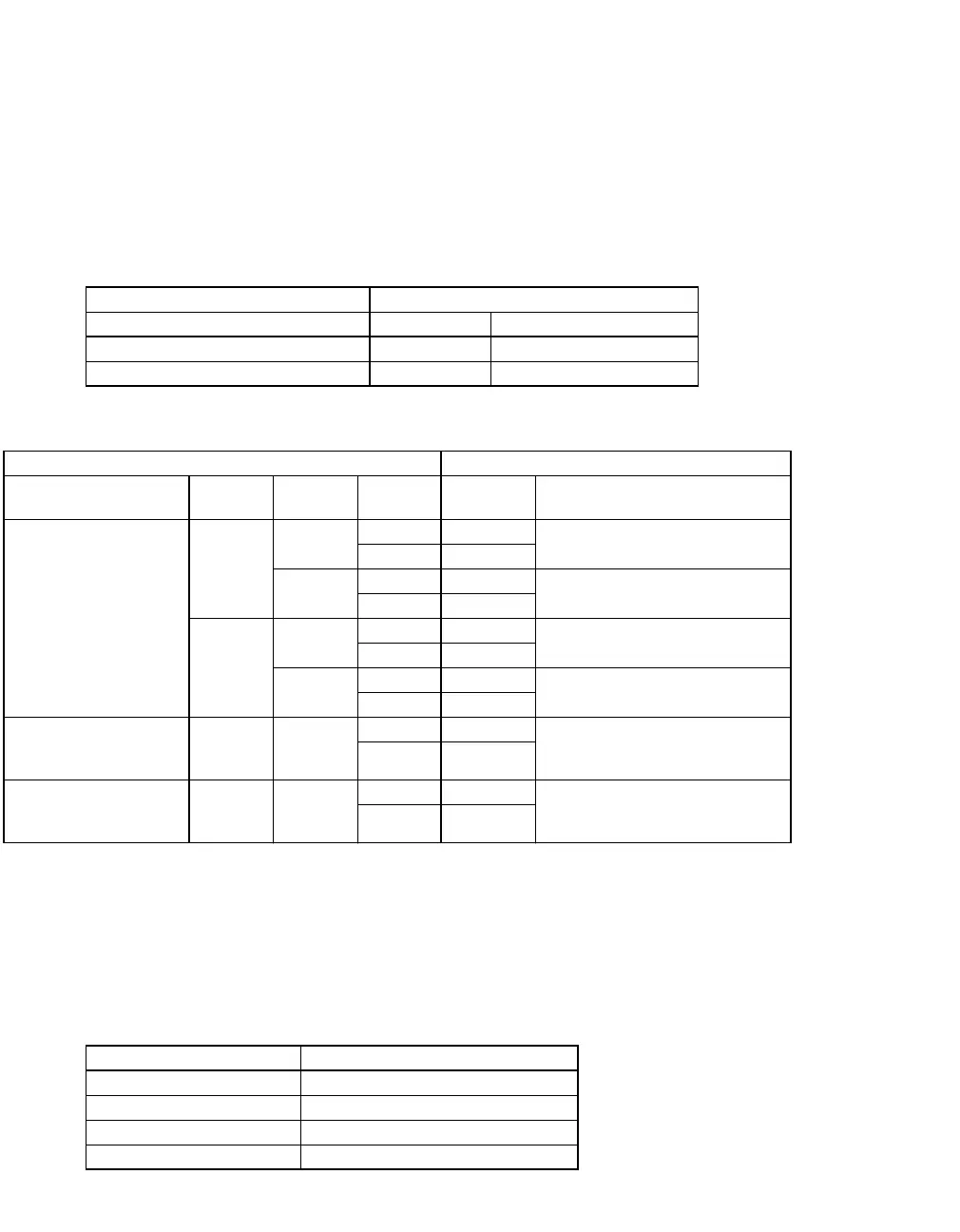

Table 6-6 ASI Mapping for Instruction Accesses

Condition for Instruction Access Resulting Action

PSTATE.TL Endianness ASI Value (in SFSR)

0 Big ASI_PRIMARY

> 0 Big ASI_NUCLEUS

Table 6-7 ASI Mapping for Data Accesses

Condition for Data Access Access Processed with:

Opcode

PSTATE.

TL

PSTATE.

CLE

D-MMU.

IE

Endianness

ASI Value

(Recorded in SFSR)

LD/ST/Atomic/FLUSH

0

0

0 Big

ASI_PRIMARY

1 Little

1

0 Little

ASI_PRIMARY_LITTLE

1 Big

> 0

0

0 Big

ASI_NUCLEUS

1 Little

1

0 Little

ASI_NUCLEUS_LITTLE

1 Big

LD/ST/Atomic Alternate

with specified ASI not

ending in “_LITTLE”

Don’t Care Don’t Care

0 Big

1

Specified ASI value from immediate

field in opcode or ASI register

1 Little

1

LD/ST/Atomic Alternate

with specified ASI

ending in ‘_LITTLE”

Don’t Care Don’t Care

0 Little

Specified ASI value from immediate

field in opcode or ASI register

1 Big

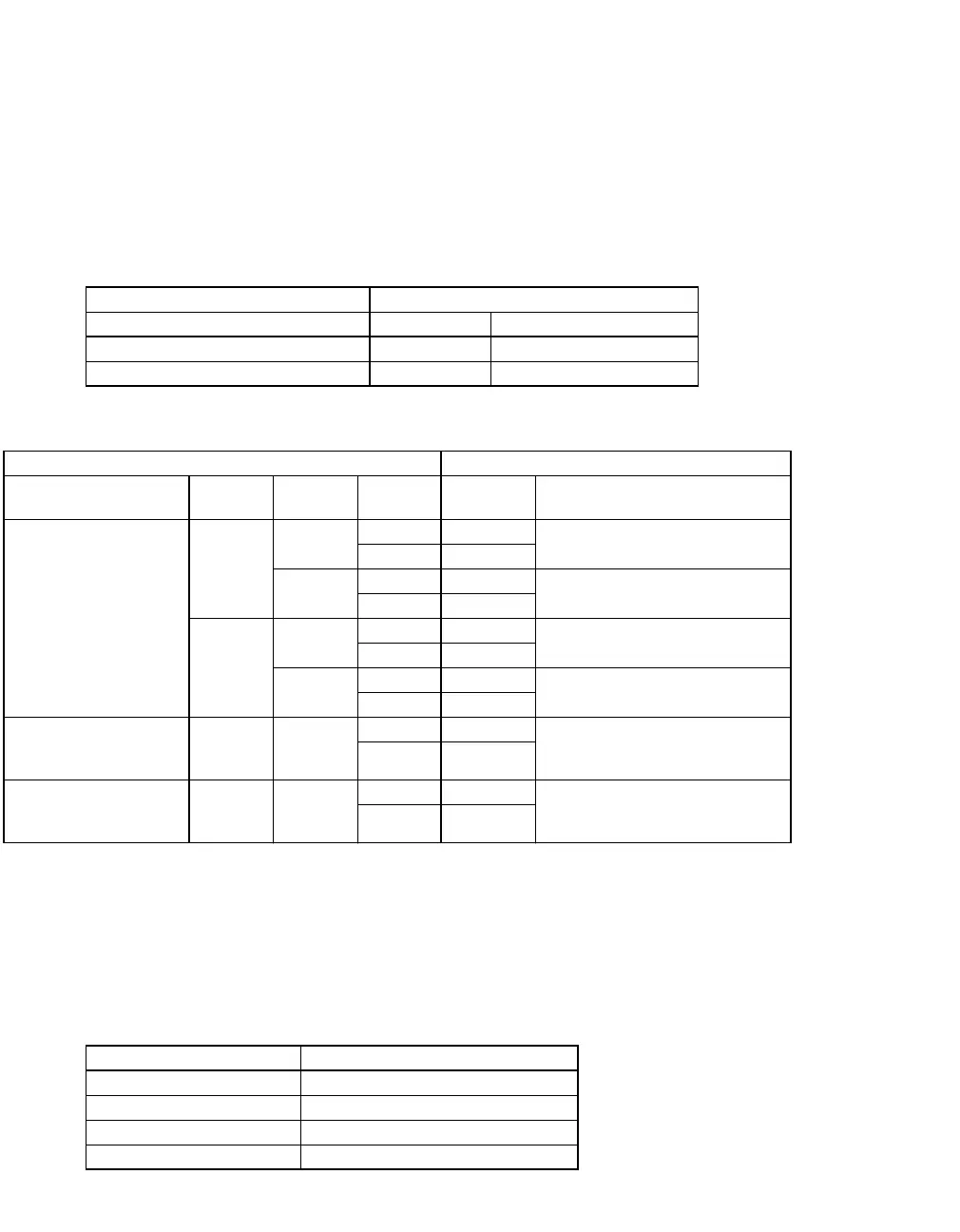

Table 6-8 I-MMU and D-MMU Context Register Usage

ASI Value Context Register

ASI_*NUCLEUS*

a

Nucleus (0000

16

hard-wired)

ASI_*PRIMARY*

b

Primary

ASI_*SECONDARY*

c

Secondary

All other ASI values (Not applicable, no translation)

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...