Sun Microelectronics

64

UltraSPARC User’s Manual

The I-/D-TSB 8 Kb/64 Kb Pointer registers are defined as follows:

Figure 6-11 I-/D-MMU TSB 8 Kb/64 Kb Pointer and D-MMU Direct Pointer Register

VA<63:0>: The full virtual address of the TTE in the TSB, as determined by the

MMU hardware. Described in Section 6.3.1, “Hardware Support for TSB

Access,” on page 45. Note that this field is sign-extended based on

VA<43>.

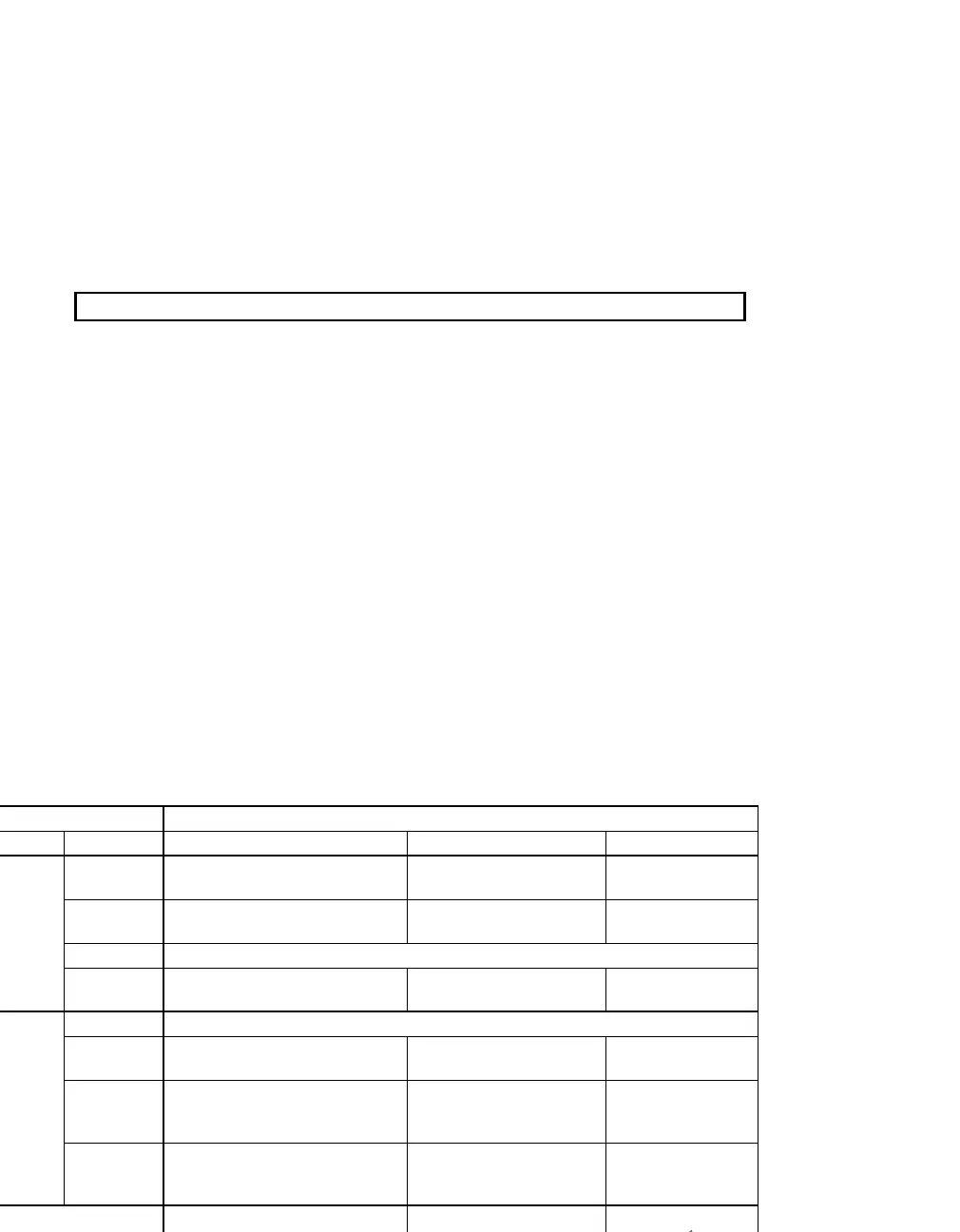

6.9.9 I-/D-TLB Data-In/Data-Access/Tag-Read Registers

Access to the TLB is complicated due to the need to provide an atomic write of a

TLB entry data item (tag and data) that is larger than 64 bits, the need to replace

entries automatically through the TLB entry replacement algorithm as well as

provide direct diagnostic access, and the need for hardware assist in the TLB miss

handler. Table 6-13 shows the effect of loads and stores on the Tag Access register

and the TLB.

Table 6-13 Effect of Loads and Stores on MMU Registers

Software Operation Effect on MMU Physical Registers

Load/Store Register TLB tag TLB data Tag Access Register

Load

Tag Read

No effect.

Contents returned

No effect No effect

Tag Access No effect No effect

No effect.

Contents returned

Data In Trap with

data_access_exception

Data Access No effect

No effect.

Contents returned

No effect

Store

Tag Read Trap with

data_access_exception

Tag Access No effect No effect

Written with store

data

Data In

TLB entry determined by replace-

ment policy written with contents

of Tag Access Register

TLB entry determined by

replacement policy written

with store data

No effect

Data Access

TLB entry specified by STXA

address written with contents of

Tag Access Register

TLB entry specified by

STXA address written with

store data

No effect

TLB miss No effect No effect

Written with VA and

context of access

63 0

VA<63:0>

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...