Chapter 7 Deployment of the CPU 21xDP Manual VIPA CPU 21x

7-24 HB103E - Rev. 05/45

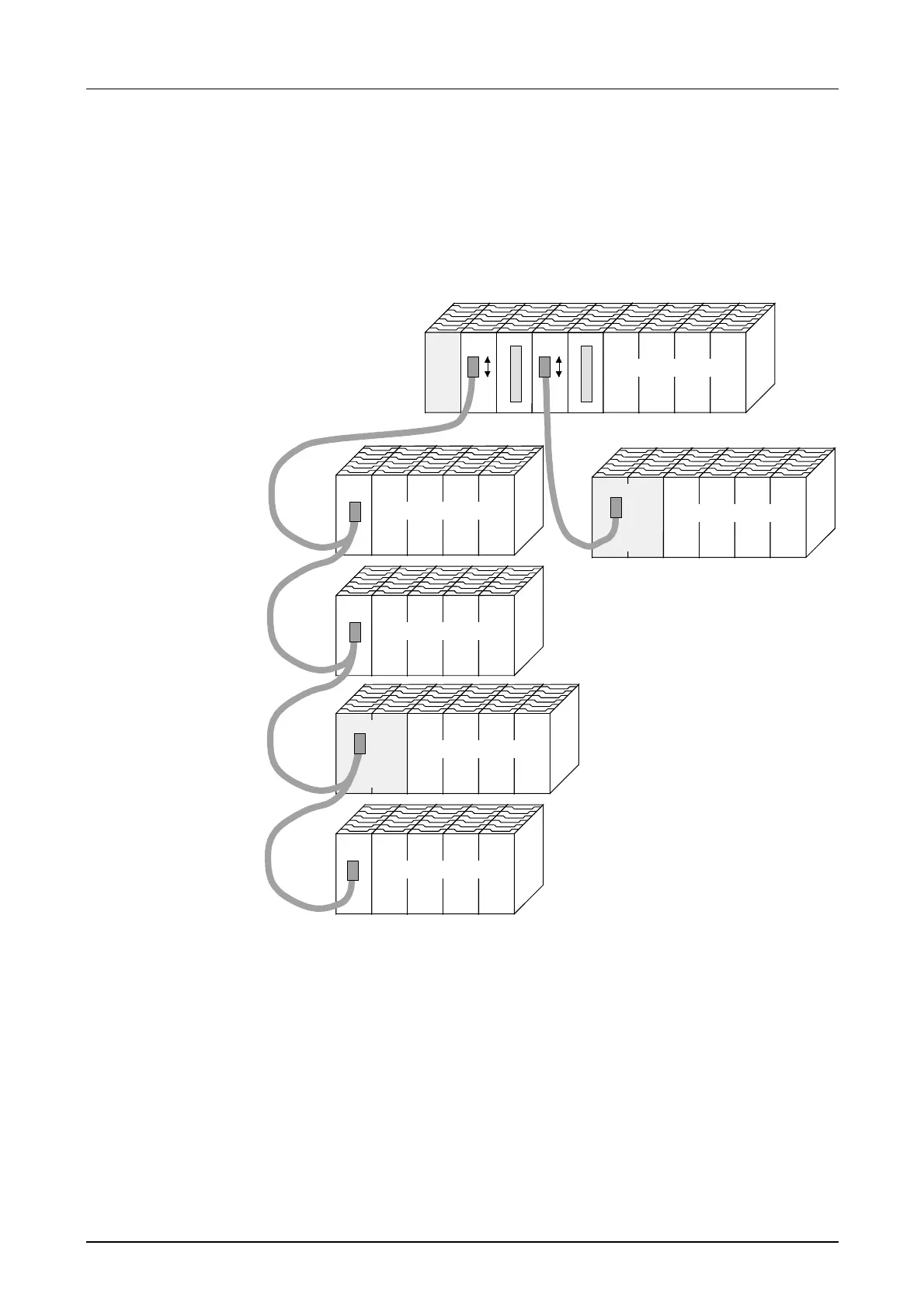

One CPU and several master interfaces

The CPU should have a short cycle time to ensure that the data of slave

No.5 (at the right) is always up to date. This scheme is only viable if the

slower line (at the left) is connected to slaves that do not require up to date

data. This portion of the line should also not be connected to modules that

issue alarms.

3

Input/output periphery

CPU 21x DP

IM 253

1

Input/output periphery

IM 253

2

Input/output periphery

IM 253

4

Input/output periphery

5

Input/output periphery

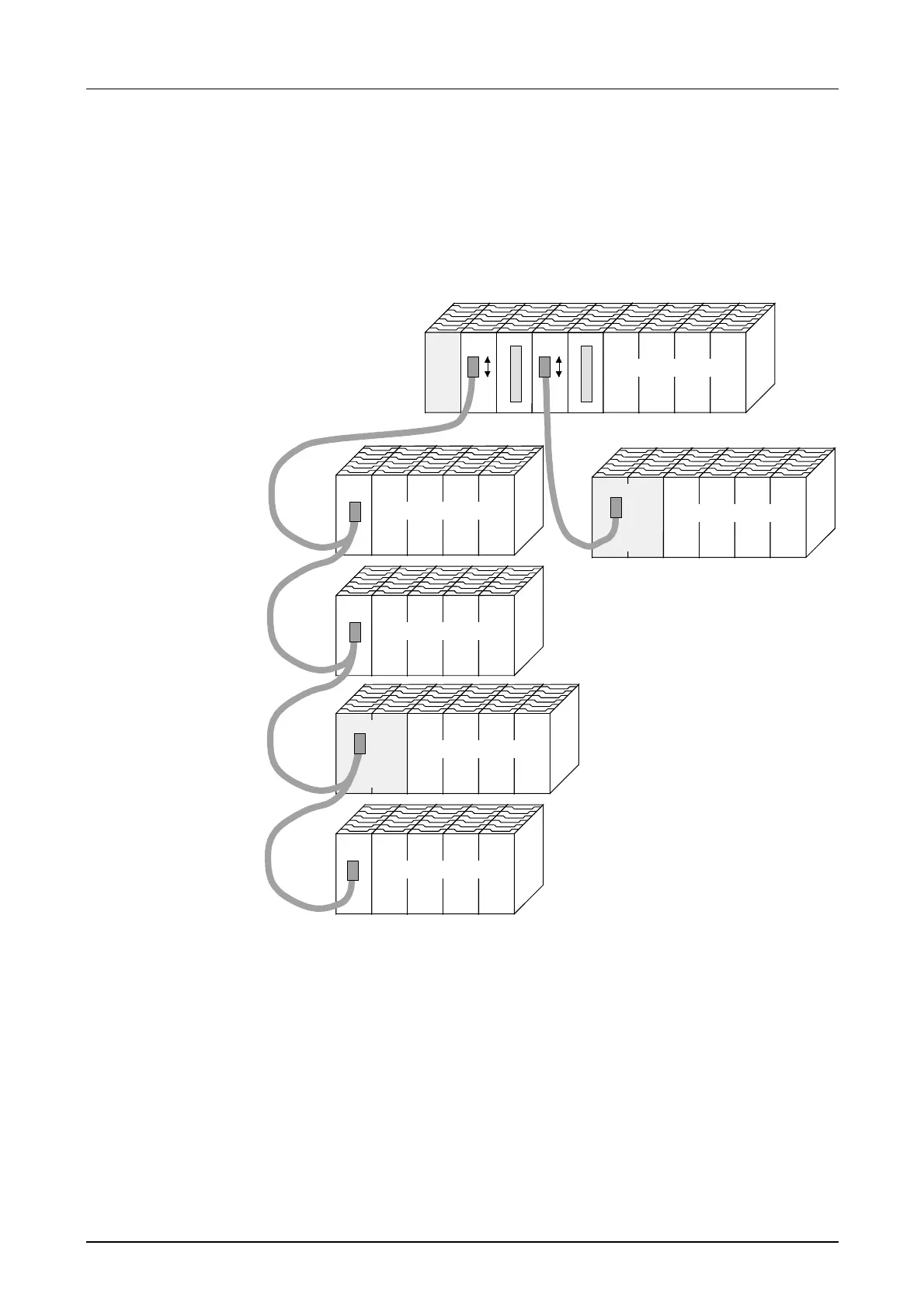

CPU IM 208

1,2,

3,4

IM 208

5

CPU 21x DP

Profibus Master

Input/output periphery

Examples for

Profibus networks

Loading...

Loading...