Test patternTest pattern

Clock ConfigurationClock Configuration

Available number of lanesAvailable number of lanes

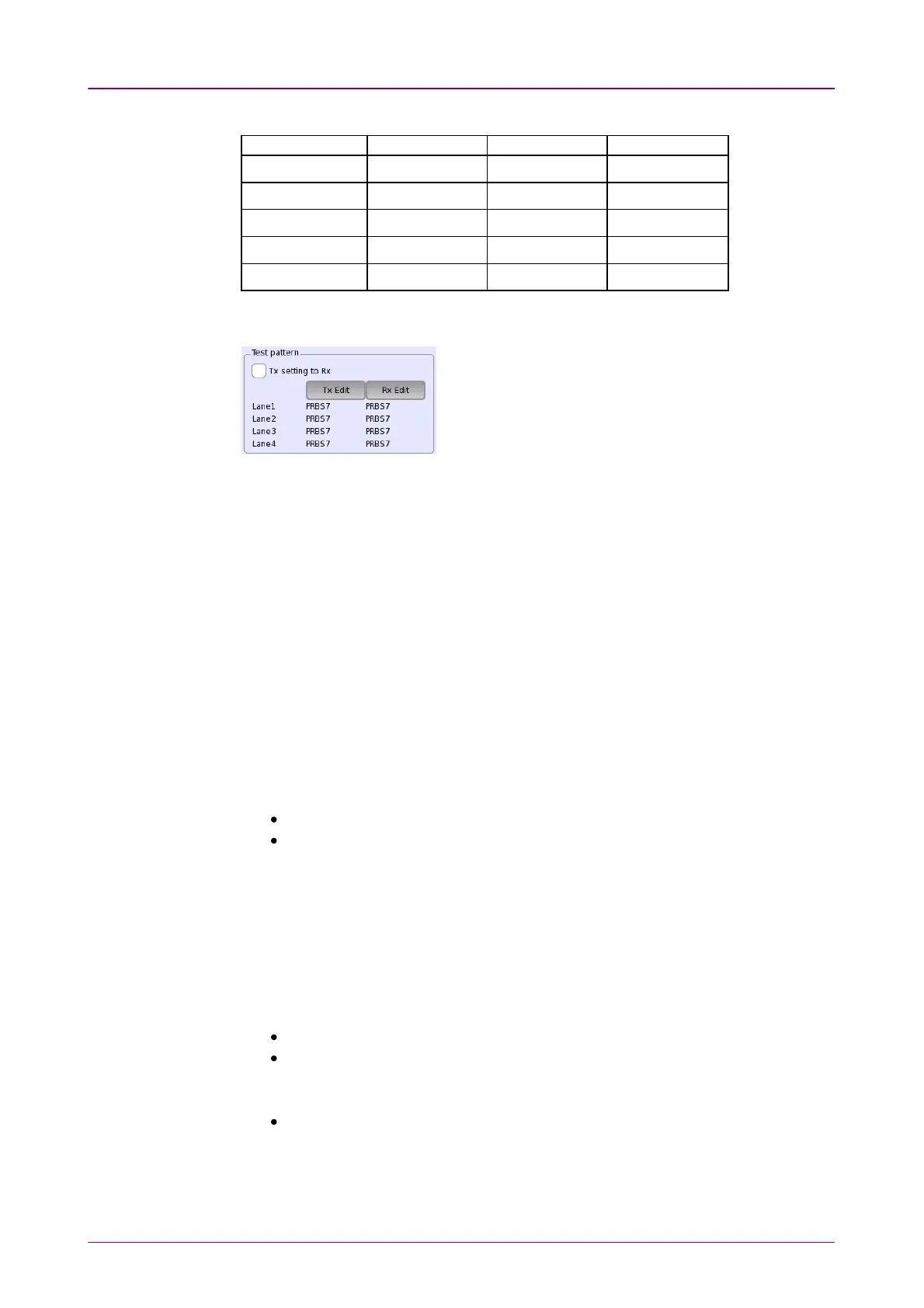

Interface TypeInterface Type MU104011AMU104011A MU104014AMU104014A MU104015AMU104015A

QSFP+ 4 4 4

QSFP28 4, 20 4, 20 4, 20

QSFP56 - 4, 8 -

QSFP-DD - 8, 16 -

OSFP - - 8, 16

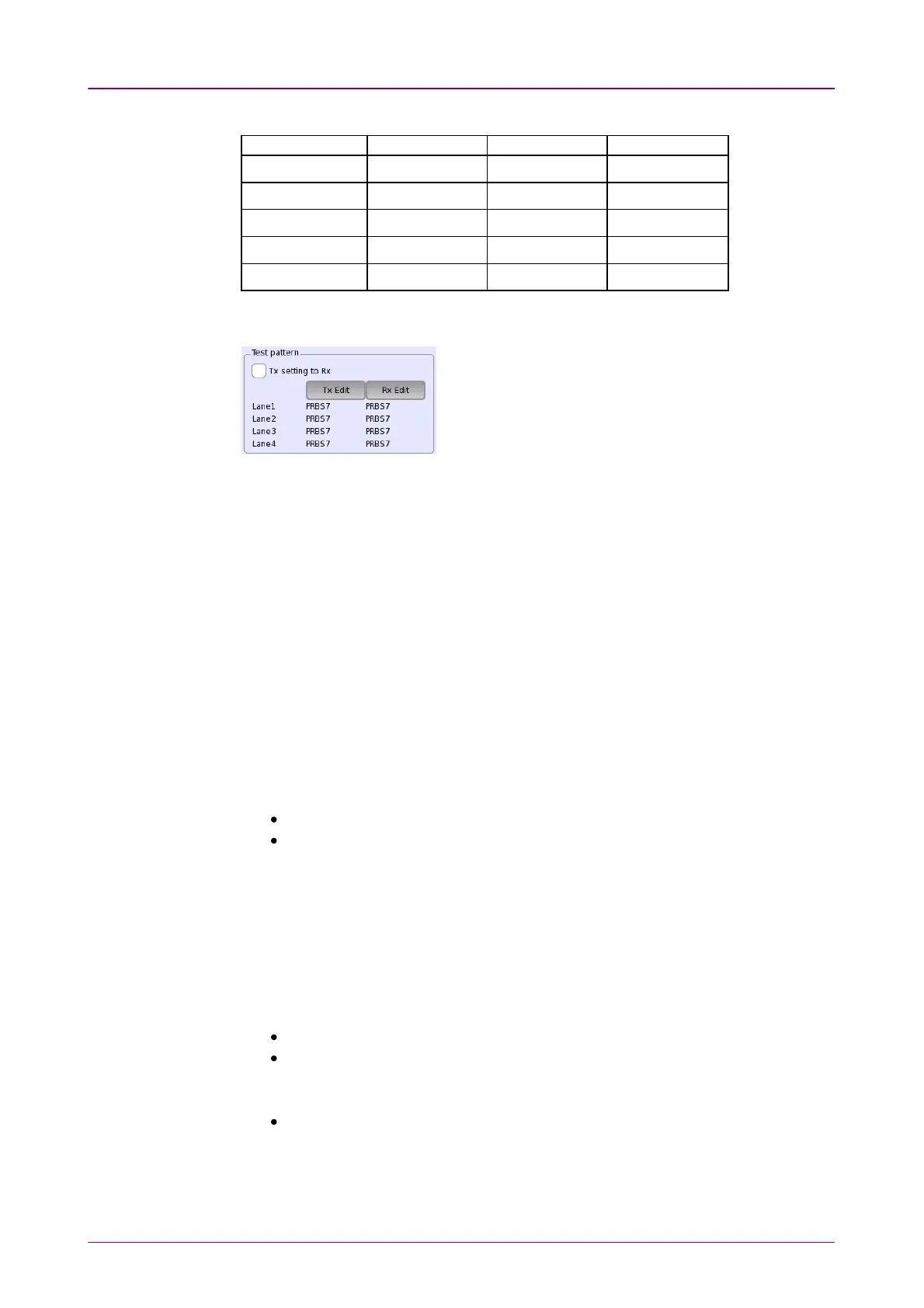

Touch the button to launch the dialog box for setting the test pattern. When

selecting Tx setting to RxTx setting to Rx, Rx pattern will be set to the same as Tx pattern.

When Lane Select is set to 4 Lanes4 Lanes, 4 Lanes (PAM4)4 Lanes (PAM4), 88

Lanes (Logical)Lanes (Logical), 8 Lanes (PAM4)8 Lanes (PAM4), or 16 Lanes (Logical)16 Lanes (Logical),

you can set patterns for each lane.

Tx Pattern:

PRBS7, PRBS9, PRBS15, PRBS23, PRBS31, Square

Wave

Rx Pattern:

PRBS7, PRBS9, PRBS15, PRBS23, PRBS31

When Bit Rate is set to 200G Ethernet200G Ethernet or 400G Ethernet400G Ethernet, available test pattern

depends on Lane Select setting:

4 Lane (PAM4), 8 Lane (PAM4)

Tx: PRBS13Q, PRBS31Q, Square Wave

Rx: PRBS13Q, PRBS31Q

8 Lane (Logical), 16 Lane (Logical)

Tx: PRBS7, PRBS9, PRBS13, PRBS15, PRBS23, PRBS31

Rx: PRBS7, PRBS9, PRBS13, PRBS15, PRBS23, PRBS31

Timing sourceTiming source

The possible sources are:

InternalInternal

ExternalExternal

When ExternalExternal is set, the right hand lamp indicates whether clock is detected or

not.

Sync PortSync Port

This item appears when Interface Type is set to SFP28SFP28, QSFP28QSFP28, QSFP56QSFP56,

QSFP-DDQSFP-DD, or OSFPOSFP. Selects the output of Sync Clock Output connector on the

module panel.

OffOff: does not output the clock.

1/81/8: outputs 1/8 divided clock of the 25/28 Gbps data synchronized clock.

For 200G Ethernet and 400G Ethernet, outputs 1/8 divided clock of the

baudrate.

1/161/16: outputs 1/16 divided clock of the 25/28 Gbps data synchronized clock.

For 200G Ethernet and 400G Ethernet, outputs 1/16 divided clock of the

baudrate.

Loading...

Loading...