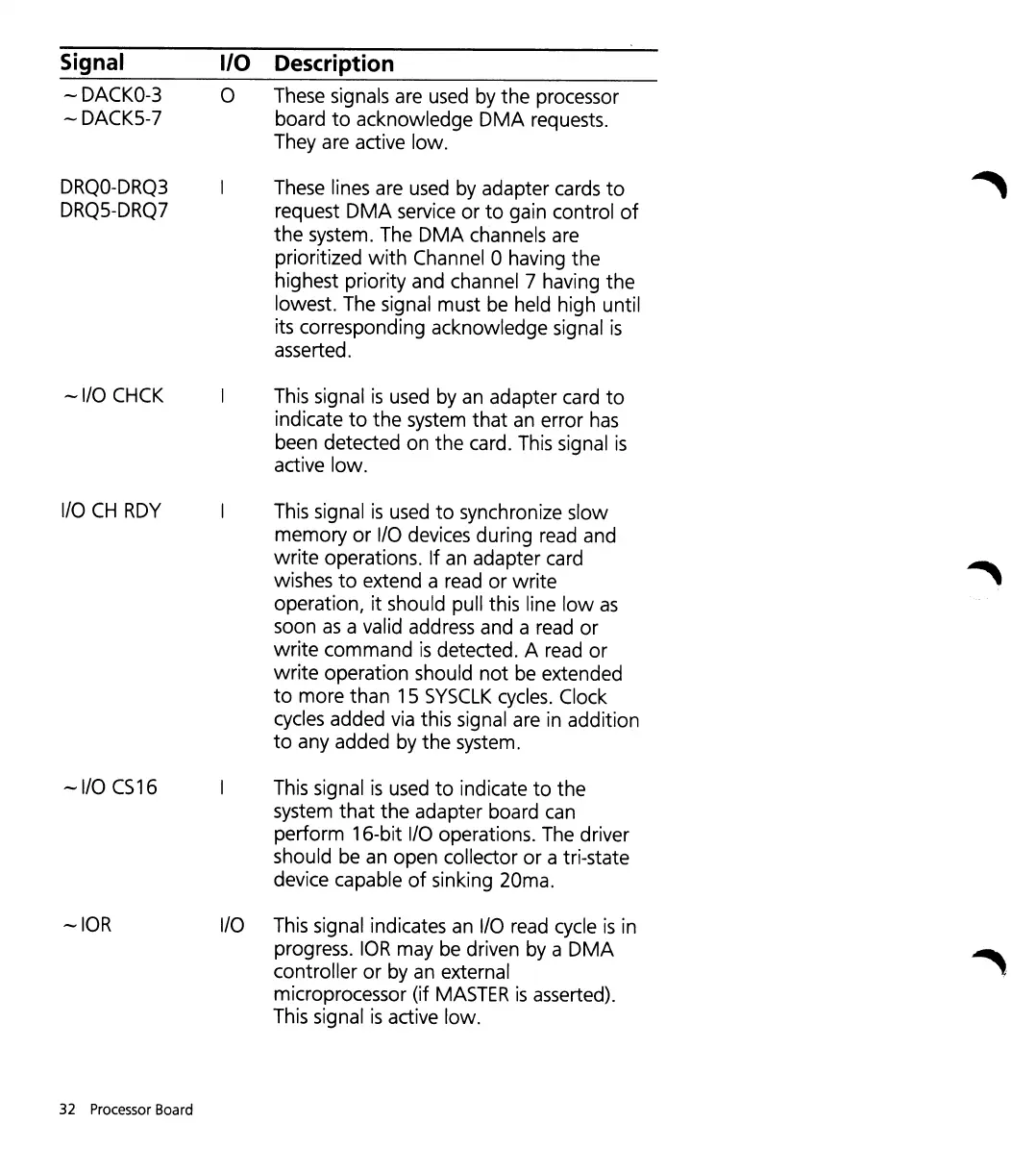

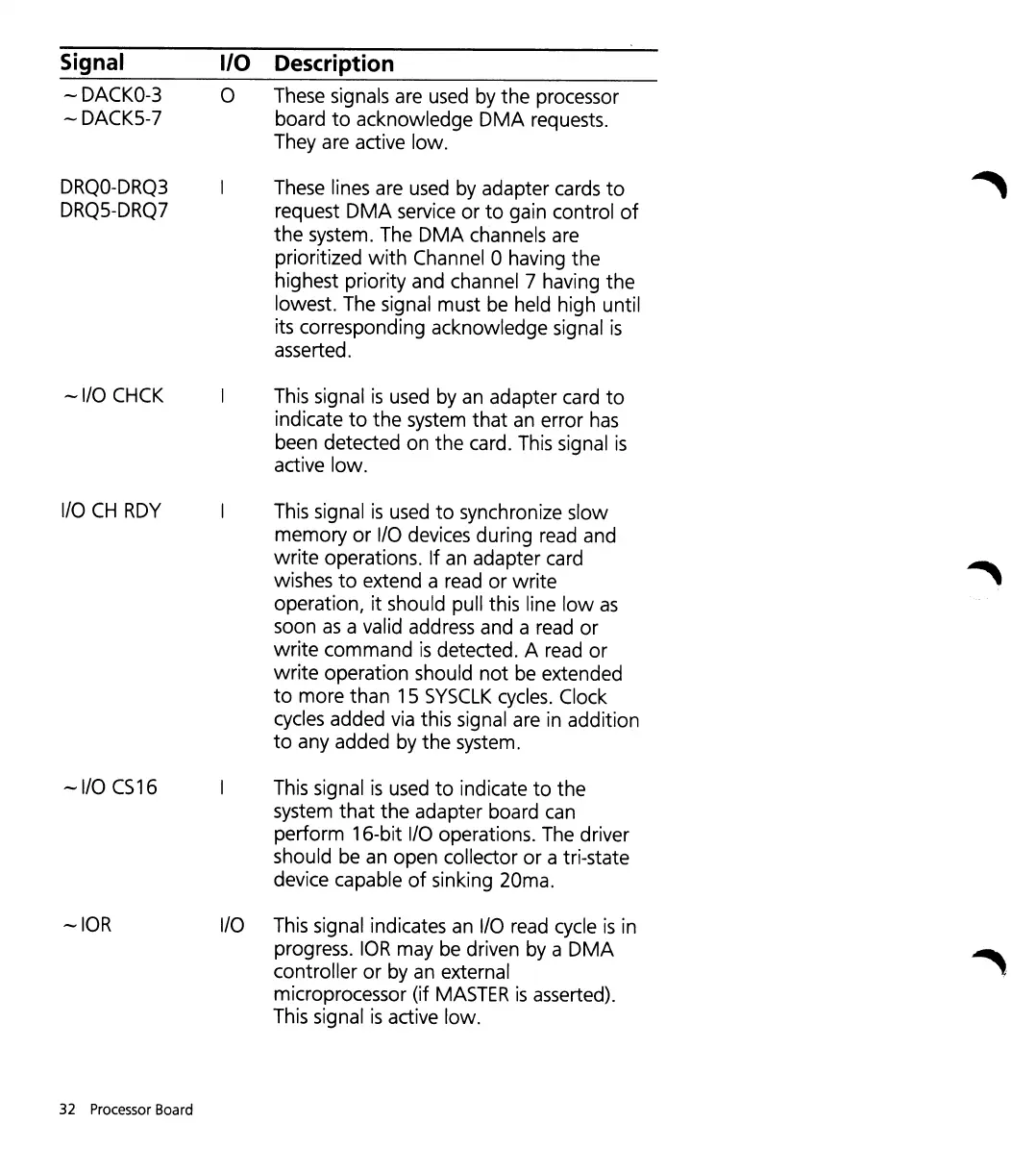

Signal

I/O Description

-DACKO-3

0

These signals are

used

by

the

processor

-DACK5-7

board

to

acknowledge

DMA

requests.

They are active low.

DRQO-DRQ3

These lines are

used

by adapter cards

to

DRQ5-DRQ7

request

DMA

service

or

to

gain control

of

the

system. The

DMA

channels are

prioritized

with

Channel 0 having

the

highest priority and channel 7 having

the

lowest. The signal must be held high until

its corresponding acknowledge signal

is

asserted.

-I/O

CHCK

This signal

is

used by

an

adapter card

to

indicate

to

the

system

that

an

error

has

been detected on

the

card. This signal

is

active low.

I/O

CH

RDY

This signal

is

used

to

synchronize slow

memory

or

I/O devices during read and

write

operations. If

an

adapter card

~

wishes

to

extend a read

or

write

operation, it should pull this line

low

as

soon

as

a valid address and a read

or

write

command

is

detected. A read

or

write

operation should

not

be extended

to

more than 15

SYSCLK

cycles.

Clock

cycles added

via

this signal are in addition

to

any added by

the

system.

-I/O

C516

This signal

is

used

to

indicate

to

the

system

that

the

adapter board can

perform 16-bit I/O operations. The driver

should be

an

open collector

or

a tri-state

device capable

of

sinking 20ma.

-lOR

I/O

This signal indicates

an

I/O read cycle

is

in

progress.

lOR

may be driven by a

DMA

~

controller

or

by

an

external

microprocessor (if

MASTER

is

asserted).

This signal

is

active low.

32

Processor

Boa

rd

Loading...

Loading...