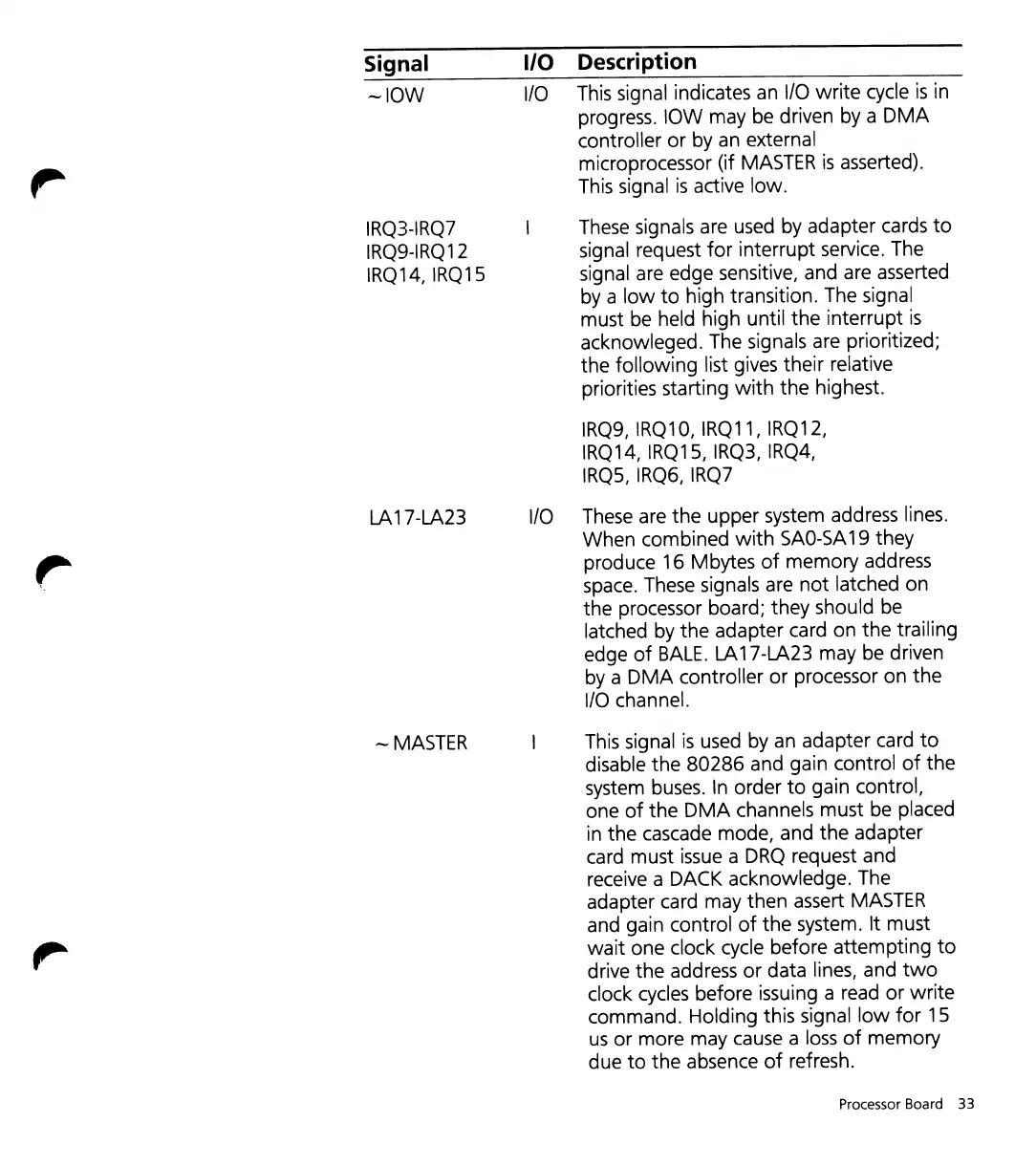

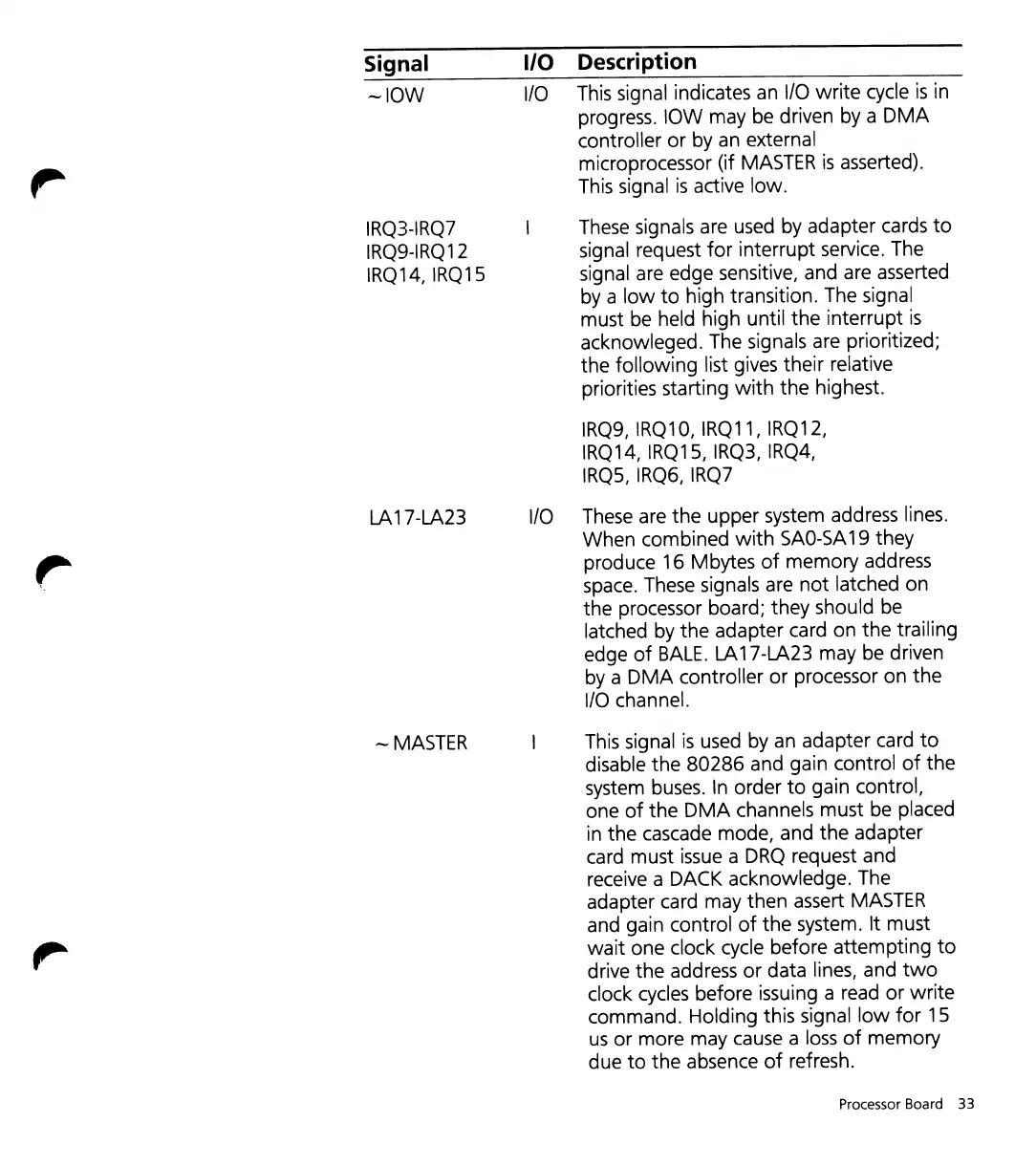

Sigrlal

-lOW

IRQ3-IRQ7

IRQ9-IRQ12

IRQ14,IRQ15

LA

17-LA23

-

MASTER

I/O Description

I/O

This signal indicates an I/O

write

cycle

is

in

progress. lOW may be driven by a

DMA

controller

or

by

an

external

microprocessor (if

MASTER

is

asserted).

This signal

is

active low.

These signals are used by adapter cards

to

signal request

for

interrupt service. The

signal are edge sensitive, and are asserted

by a

low

to

high transition. The signal

must be held high until

the

interrupt

is

acknowleged. The signals are prioritized;

the following list gives their relative

priorities starting

with

the

highest.

IRQ9,

IRQ10, IRQ11, IRQ12,

IRQ14, IRQ15,

IRQ3,

IRQ4,

IRQ5,

IRQ6,

IRQ7

I/O

These are

the

upper system address lines.

When combined

with

SAO-SA

19 they

produce 16 Mbytes

of

memory address

space. These signals are

not

latched on

the processor board; they should be

latched by

the

adapter card on

the

trailing

edge

of

BALE.

LA

17-LA23 may be driven

by a

DMA

controller

or

processor on the

I/O channel.

This signal

is

used by an adapter card

to

disable

the

80286

and gain control

of

the

system buses.

In

order

to

gain control,

one

of

the

DMA

channels must be placed

in

the

cascade mode, and

the

adapter

card must

issue

a

DRQ

request and

receive a DACK acknowledge. The

adapter card may then assert

MASTER

and gain control

of

the

system. It must

wait

one clock cycle before attempting

to

drive

the

address

or

data lines, and

two

clock cycles before issuing a read

or

write

command. Holding this signal

low

for

15

us

or

more may cause a

loss

of

memory

due

to

the

absence

of

refresh.

Processor Board 33

Loading...

Loading...