CX950 Hardware Reference Manual

19-2

3021M100-002

19.1.1 SAR Controller

The Segmentation and Reassembly (SAR) controller performs segmentation o

outgoing packets and reassembly of incoming cells. It has two interfaces: one to

the standard Utopia bus for connection to the PHY device and the other to the PC

bus for connection to the main processor on the motherboard.

19.1.2 Utopia Bus

The Utopia bus is an 8-bit bi-directional parallel bus which interconnects the SAR

controller to the PHY device. The data traversing this bus is in the form of ATM

cells.

19.1.3 PCI Bus

An 80-pin card edge connector is used to connect the on-board 32-bit Peripheral

Component Interconnect (PCI) bus to the CX950 motherboard. The PCI bus

enables the high-speed transfer of data between the ATM I/O SAR Controller and

the motherboard CPU. The PCI bus is also used to transfer configuration and

status information to and from the SAR Controller’s registers.

19.1.4 SAR Memory

The SAR requires local SRAM memory for storage of cells, traffic management

tables, schedule tables, queues and temporary storage. The card can use up to

eight 64Kx16-bit memory devices for a total of 1MB of SRAM.

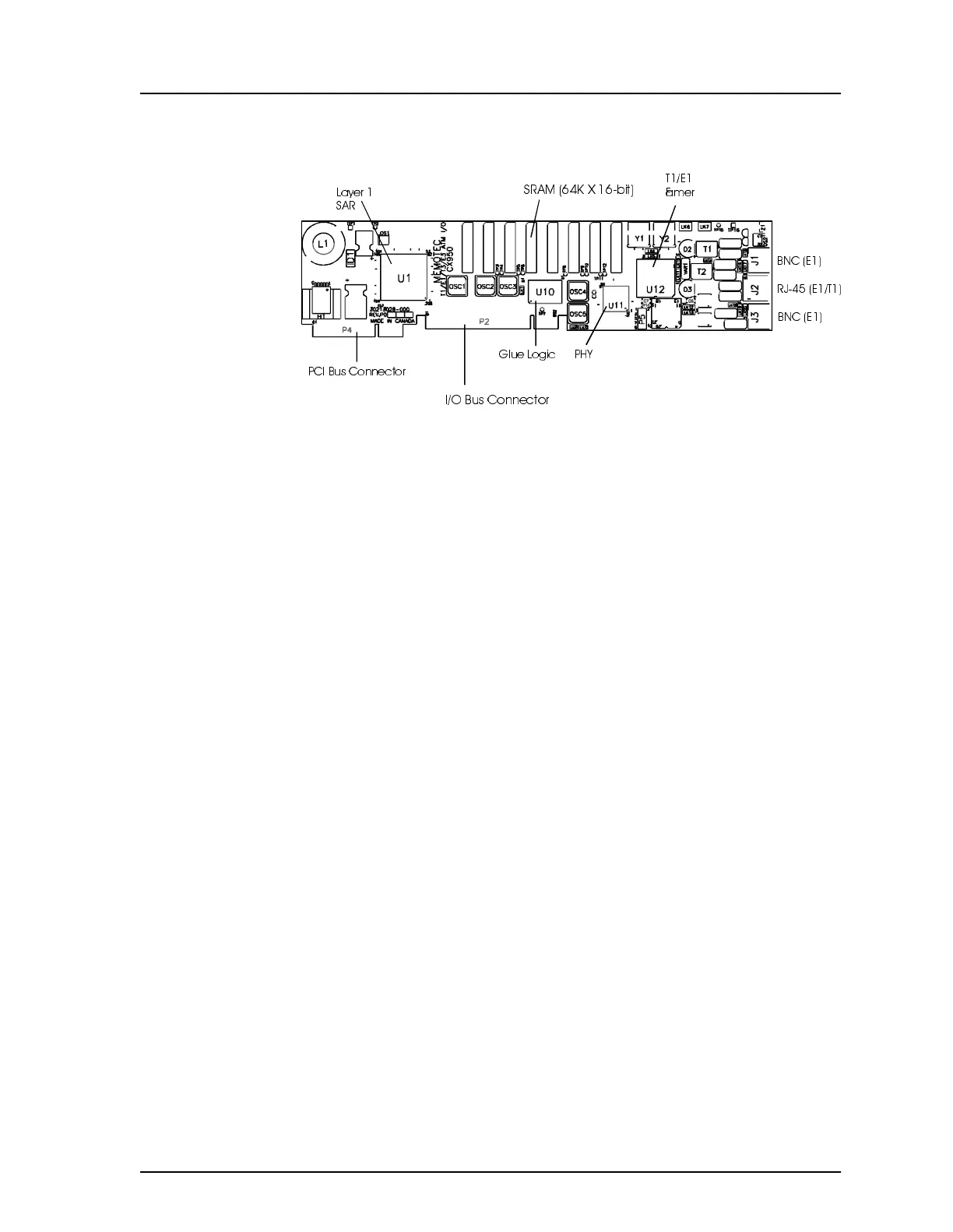

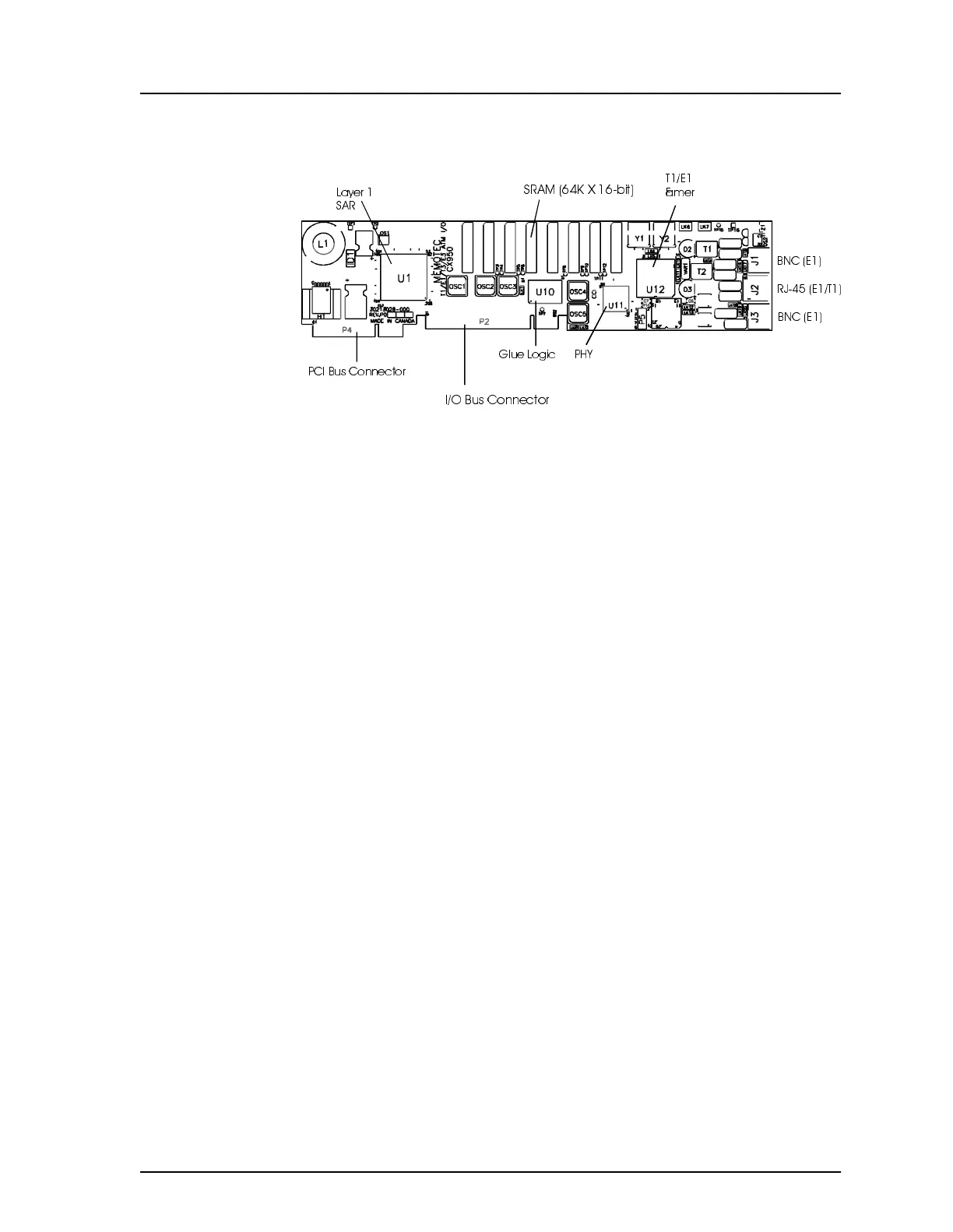

Figure 19-1 ATM I/O Card

!

"# $%

Loading...

Loading...