Remote Control

R&S

®

FPC

344User Manual 1178.4130.02 ─ 07

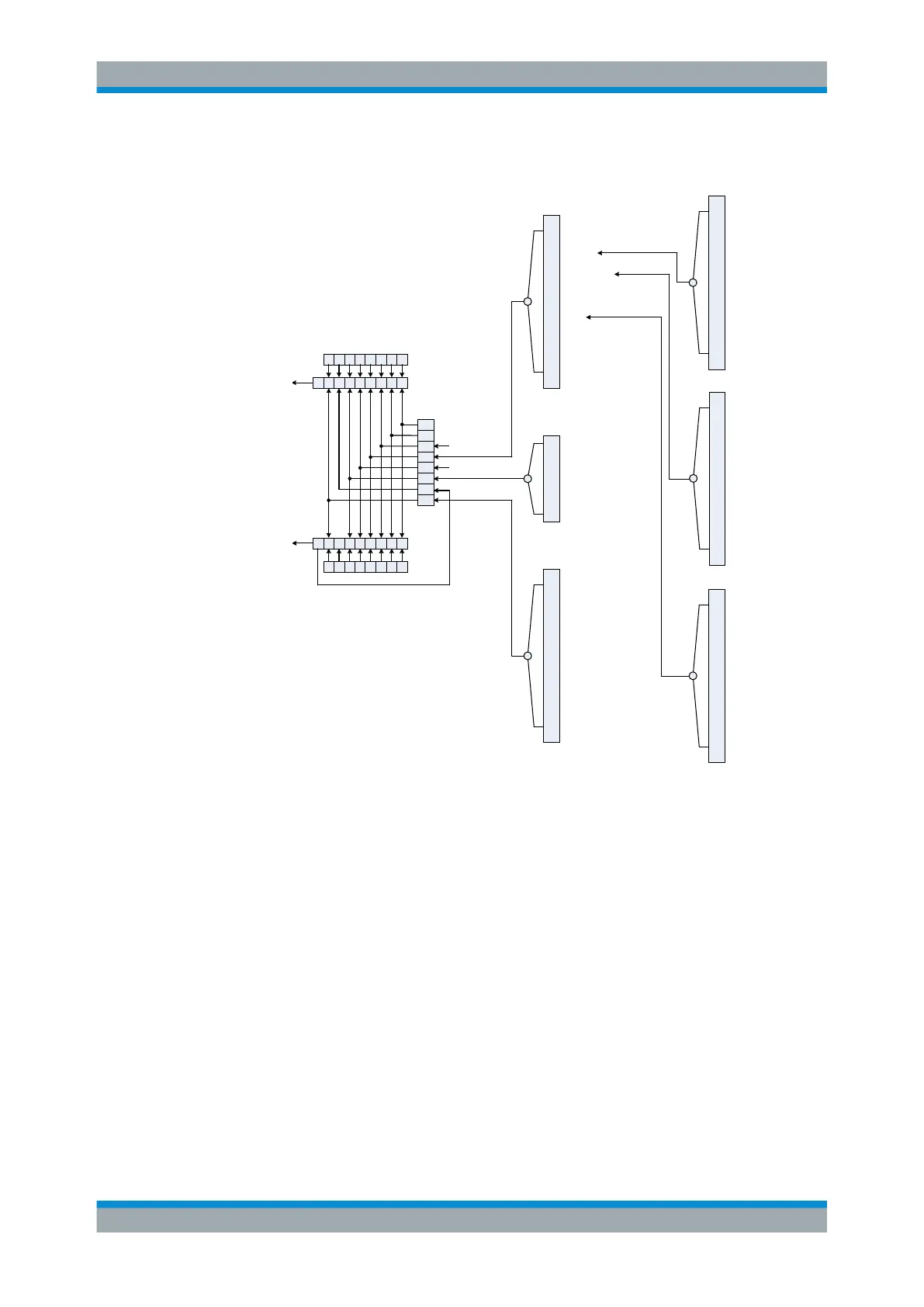

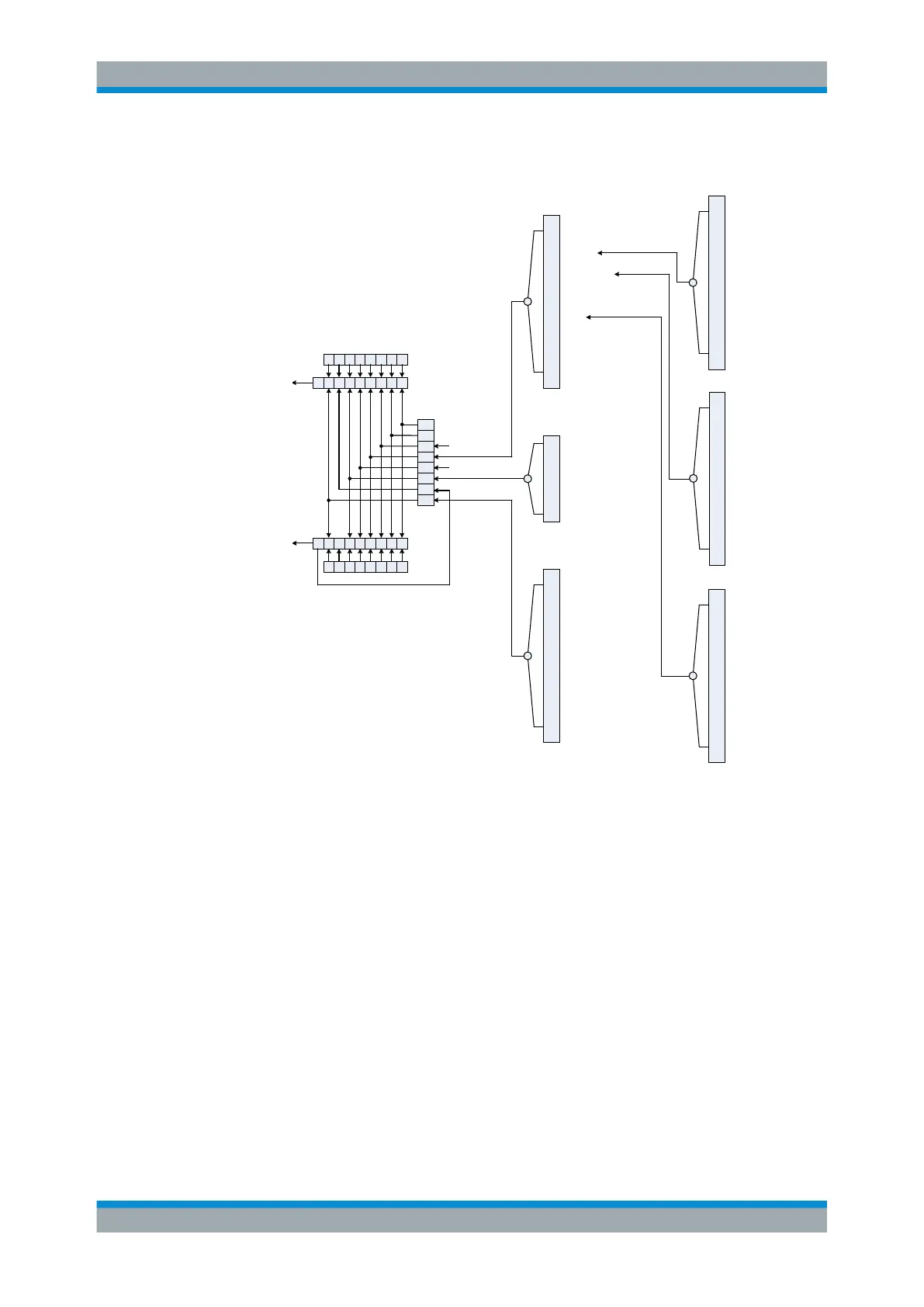

19.17.2 Overview of the Status Registers

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

not used

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

reserved

reserved

reserved

POWer

reserved

FREQuency

reserved

reserved

reserved

LIMit

reserved

reserved

reserved

reserved

reserved

not used

0

1

2

3

4

5

6

7

Error Queue

Message Queue

+

0

1

2

3

4

5

6

7

Operation Complete

reserved

Query Error

Device Dependent Error

Execution Error

Command Error

reserved

Power On

+

+

& & & & & & & &

& & & & & & & &

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

PPE

SRE

≥

1

≥

1

IST Message

SRQ Message

STB

Operation Status

Event Status Register

+ Event Status Enable

QUEStionable Status

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

EXTernalREFerence

reserved

reserved

reserved

reserved

reserved

reserved

not used

+

QUEStionable:FREQuency

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

LIMit1 FAIL

LIMit2 FAIL

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

not used

+

QUEStionable:LIMit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

reserved

reserved

IF_Overload

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

not used

+

QUEStionable:POWer

Figure 19-6: Overview of the status registers

19.17.3 Status Byte (STB) and Service Request Enable Register (SRE)

The STB is already defined in IEEE 488.2. It provides a rough overview of the instru-

ment status by collecting the pieces of information of the lower registers. It can thus be

compared with the CONDition part of an SCPI register and assumes the highest level

within the SCPI hierarchy. A special feature is that bit 6 acts as the sum bit of the

remaining bits of the status byte.

The STATUS BYTE is read using the command *STB? or a serial poll.

The STB is linked to the SRE. The latter corresponds to the ENABle part of the SCPI

registers in its function. Each bit of the STB is assigned a bit in the SRE. Bit 6 of the

SRE is ignored. If a bit is set in the SRE and the associated bit in the STB changes from

0 to 1, a service request (SRQ) is generated, which triggers an interrupt in the control-

Status Reporting System

Loading...

Loading...