The STM32 Cortex-M4 instruction set PM0214

138/262 PM0214 Rev 9

Restrictions

Do not use SP and do not use PC.

Condition flags

These instructions do not affect the flags.

Examples

SXTAH R4, R8, R6, ROR #16 ; Rotates R6 right by 16 bits, obtains bottom

; halfword, sign extends to 32 bits, adds R8,and

; writes to R4

UXTAB R3, R4, R10 ; Extracts bottom byte of R10 and zero extends to 32

; bits, adds R4, and writes to R3.

3.9 Bitfield instructions

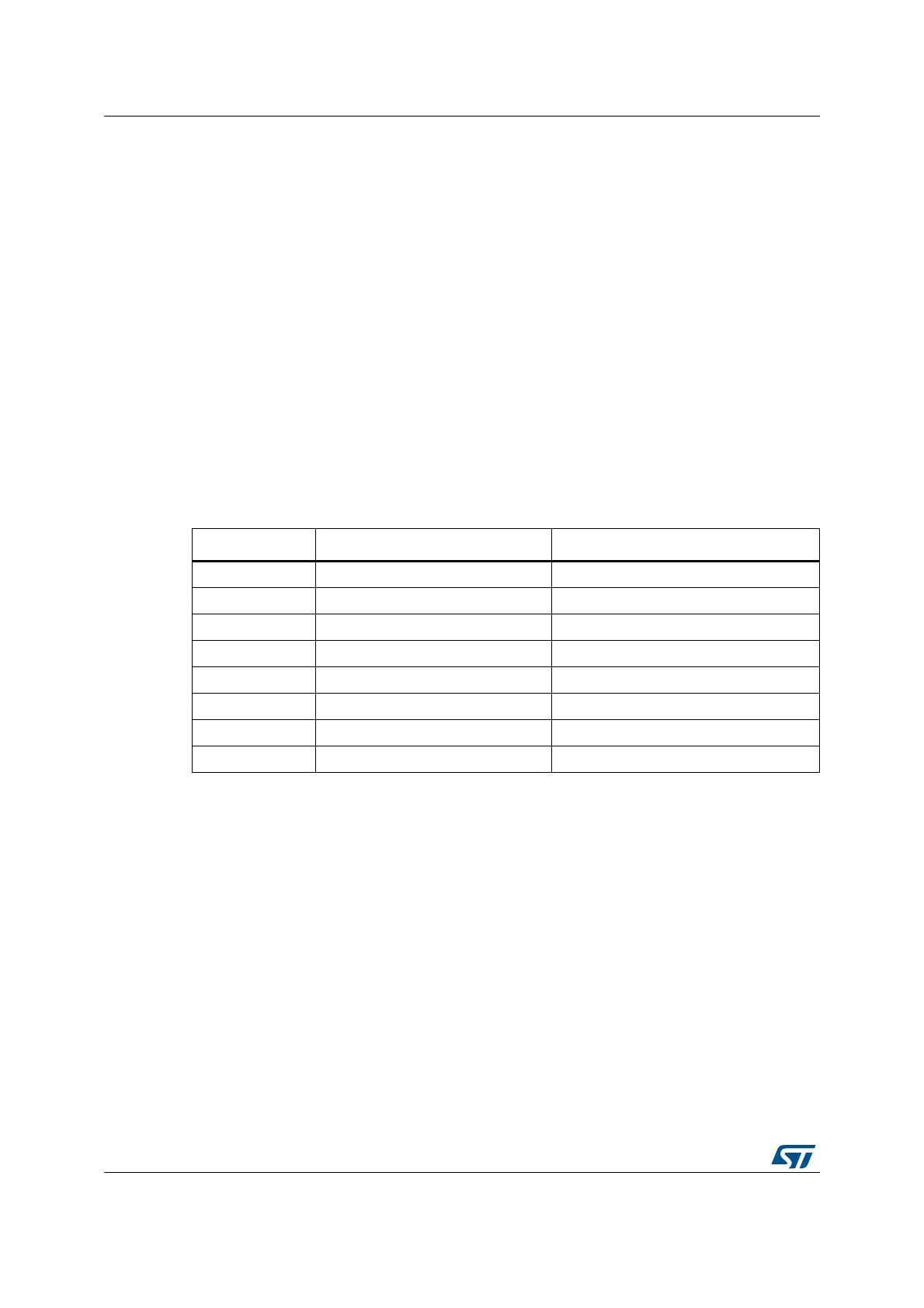

Table 32 shows the instructions that operate on adjacent sets of bits in registers or bitfields.

Table 32. Instructions that operate on adjacent sets of bits

Mnemonic Brief description See

BFC Bit field clear BFC and BFI on page 139

BFI Bit field insert BFC and BFI on page 139

SBFX Signed bit field extract SBFX and UBFX on page 140

SXTB Sign extend a byte SXT and UXT on page 141

SXTH Sign extend a halfword SXT and UXT on page 141

UBFX Unsigned bit field extract SBFX and UBFX on page 140

UXTB Zero extend a byte SXT and UXT on page 141

UXTH Zero extend a halfword SXT and UXT on page 141

Loading...

Loading...