PM0214 Rev 9 255/262

PM0214 Core peripherals

261

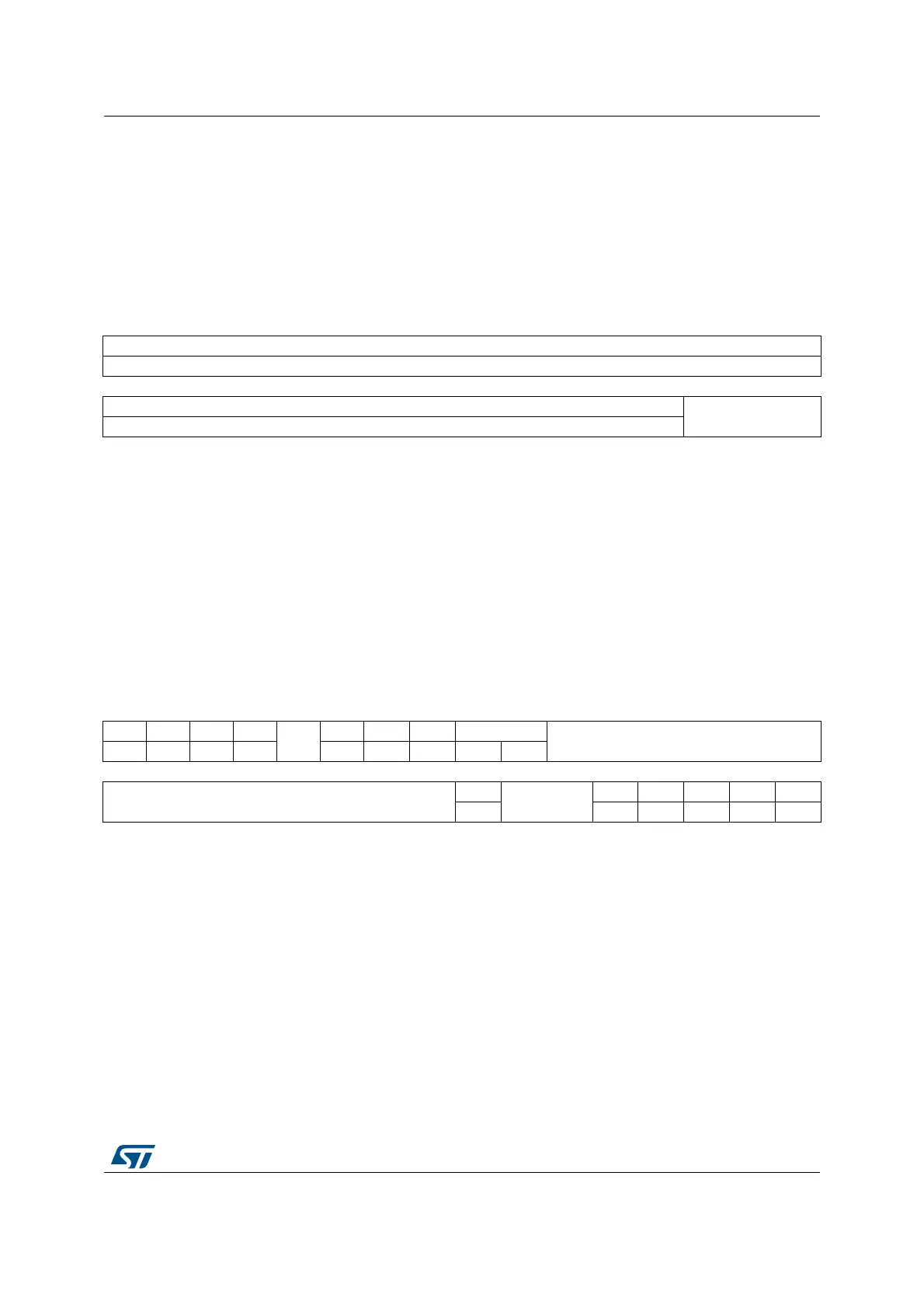

4.6.3 Floating-point context address register (FPCAR)

Address offset: 0x08

Reset value: 0x0000000

Required privilege: Privileged

The FPCAR register holds the location of the unpopulated floating-point register space

allocated on an exception stack frame.

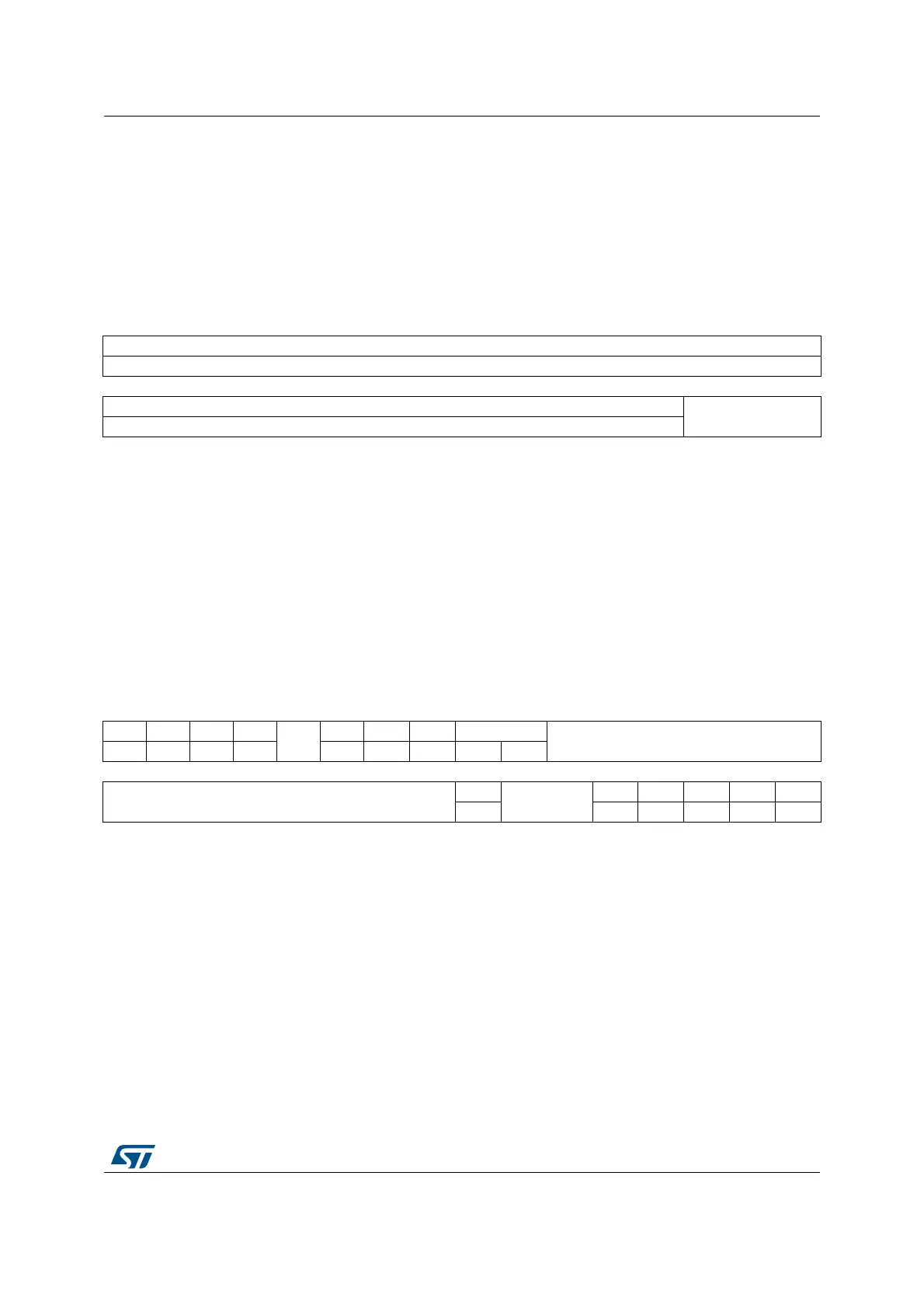

4.6.4 Floating-point status control register (FPSCR)

Address offset: Not mapped

Reset value: 0x0000000

Required privilege: Privileged

The FPSCR register provides all necessary user level control of the floating-point system.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ADDRESS[31:16]

rw

1514131211109876543210

ADDRESS[15:3]

Reserved

rw

Bits 31:3 ADDRESS: Location of unpopulated floating-point register space allocated on an exception

stack frame.

Bits 2:0 Reserved. Read as Zero, Writes Ignored.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

NZCV

Reserv

ed

AHP DN FZ RMode

Reserved

rw rw rw rw rw rw rw rw rw

1514131211109876543210

Reserved

IDC

Reserved

IXC UFC OFC DZC IOC

rw rw rw rw rw rw

Bit 31 N: Negative condition code flag. Floating-point comparison operations update these flags. For

more details on the result, refer to Table 57.

0: Operation result was positive, zero, greater than, or equal.

1: Operation result was negative or less than.

Bit 30 Z: Zero condition code flag. Floating-point comparison operations update these flags. For more

details on the result, refer to Table 57.

0: Operation result was not zero.

1: Operation result was zero.

Bit 29 C: Carry condition code flag. Floating-point comparison operations update these flags. For more

details on the result, refer to Table 57.

0: Add operation did not result in a carry bit or subtract operation resulted in a borrow bit.

1: Add operation resulted in a carry bit or subtract operation did not result in a borrow bit.

Loading...

Loading...