Core peripherals PM0214

216/262 PM0214 Rev 9

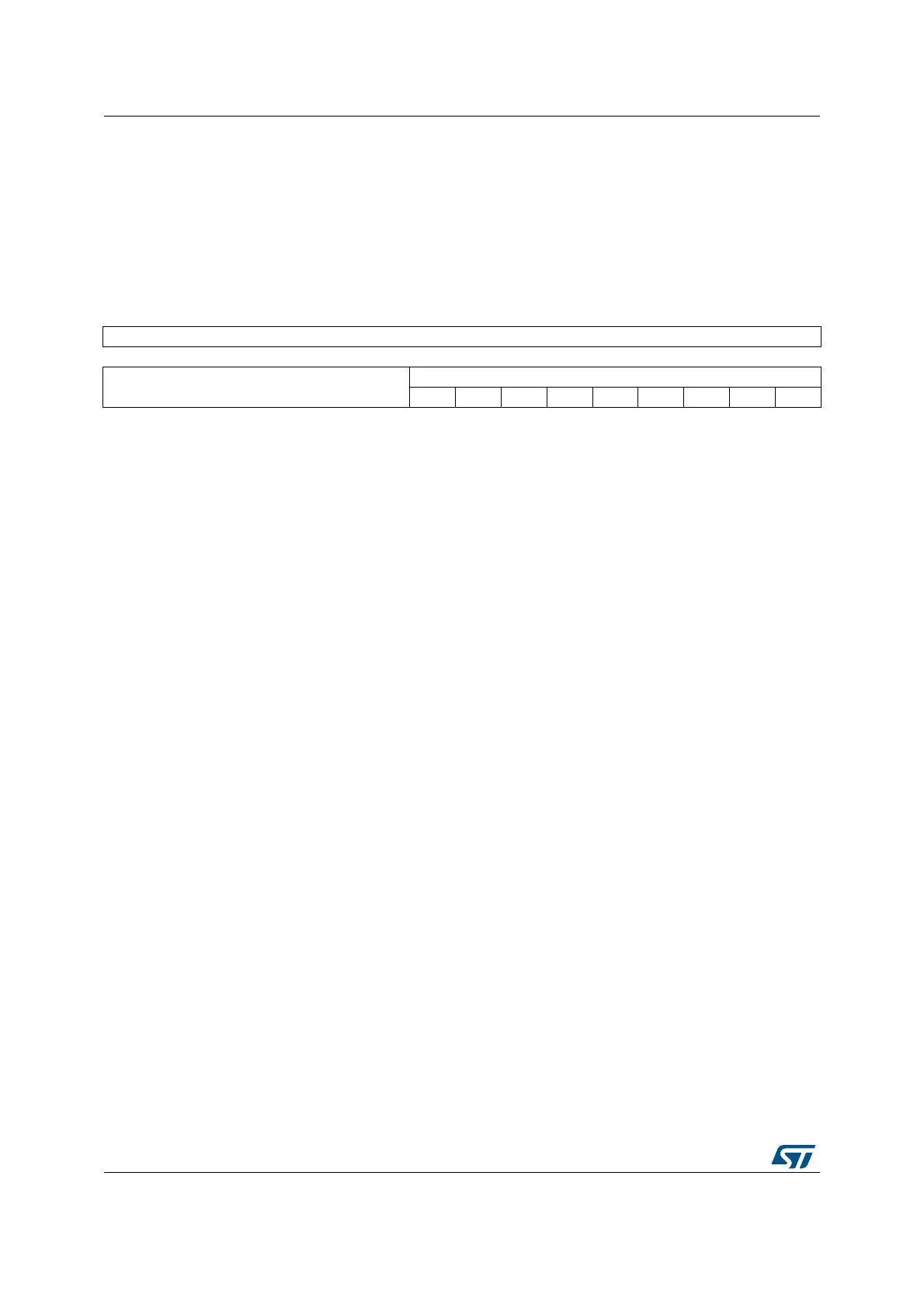

4.3.8 Software trigger interrupt register (NVIC_STIR)

Address offset: 0xE00

Reset value: 0x0000 0000

Required privilege: When the USERSETMPEND bit in the SCR is set to 1, unprivileged

software can access the STIR, see Section 4.4.6: System control register (SCR). Only

privileged software can enable unprivileged access to the STIR.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

INTID[8:0]

wwwwwwwww

Bits 31:9 Reserved, must be kept cleared.

Bits 8:0 INTID Software generated interrupt ID

Write to the STIR to generate a Software Generated Interrupt (SGI). The value to be written is

the Interrupt ID of the required SGI, in the range 0-239. For example, a value of 0x03 specifies

interrupt IRQ3.

Loading...

Loading...