The Cortex-M4 processor PM0214

20/262 PM0214 Rev 9

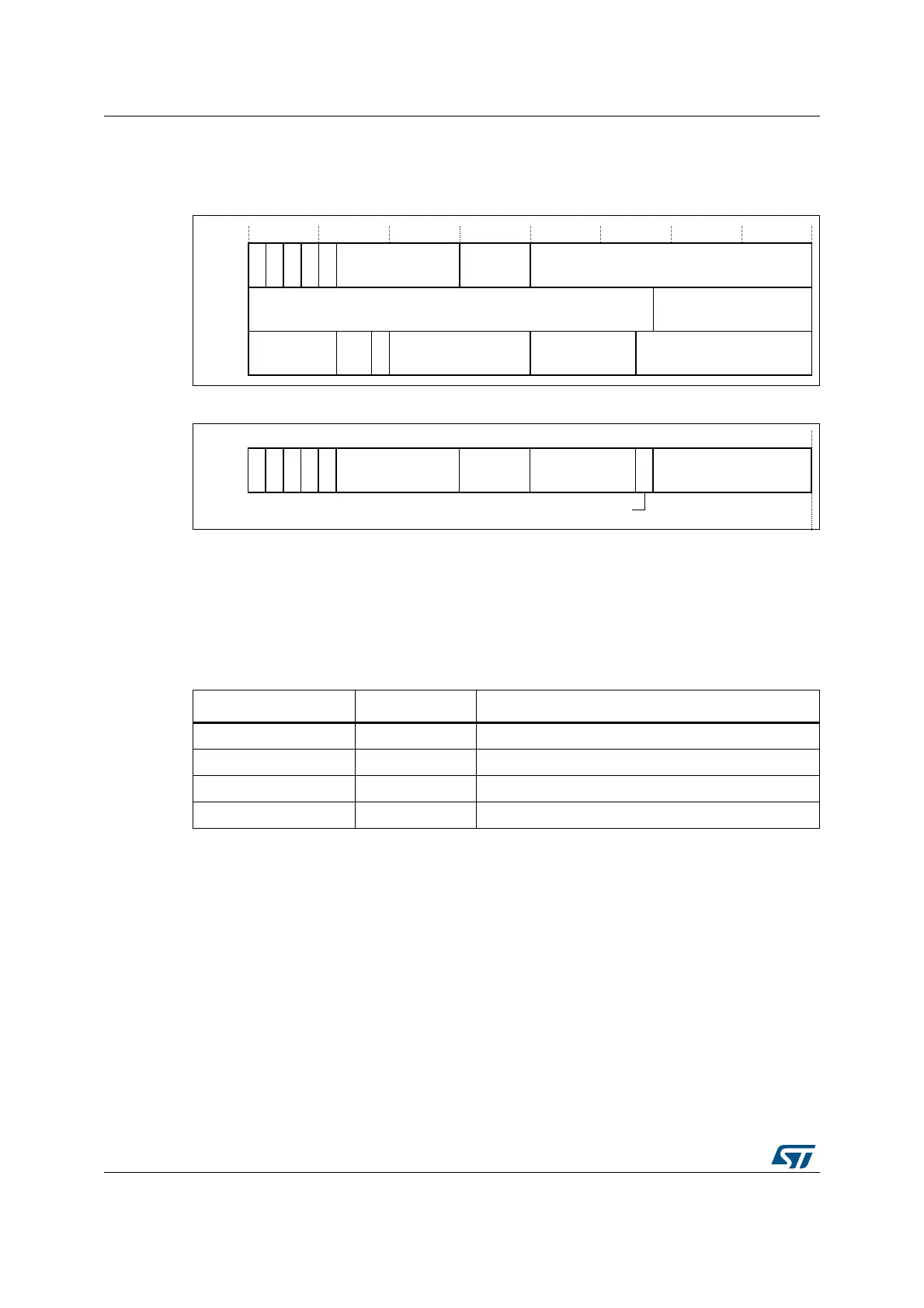

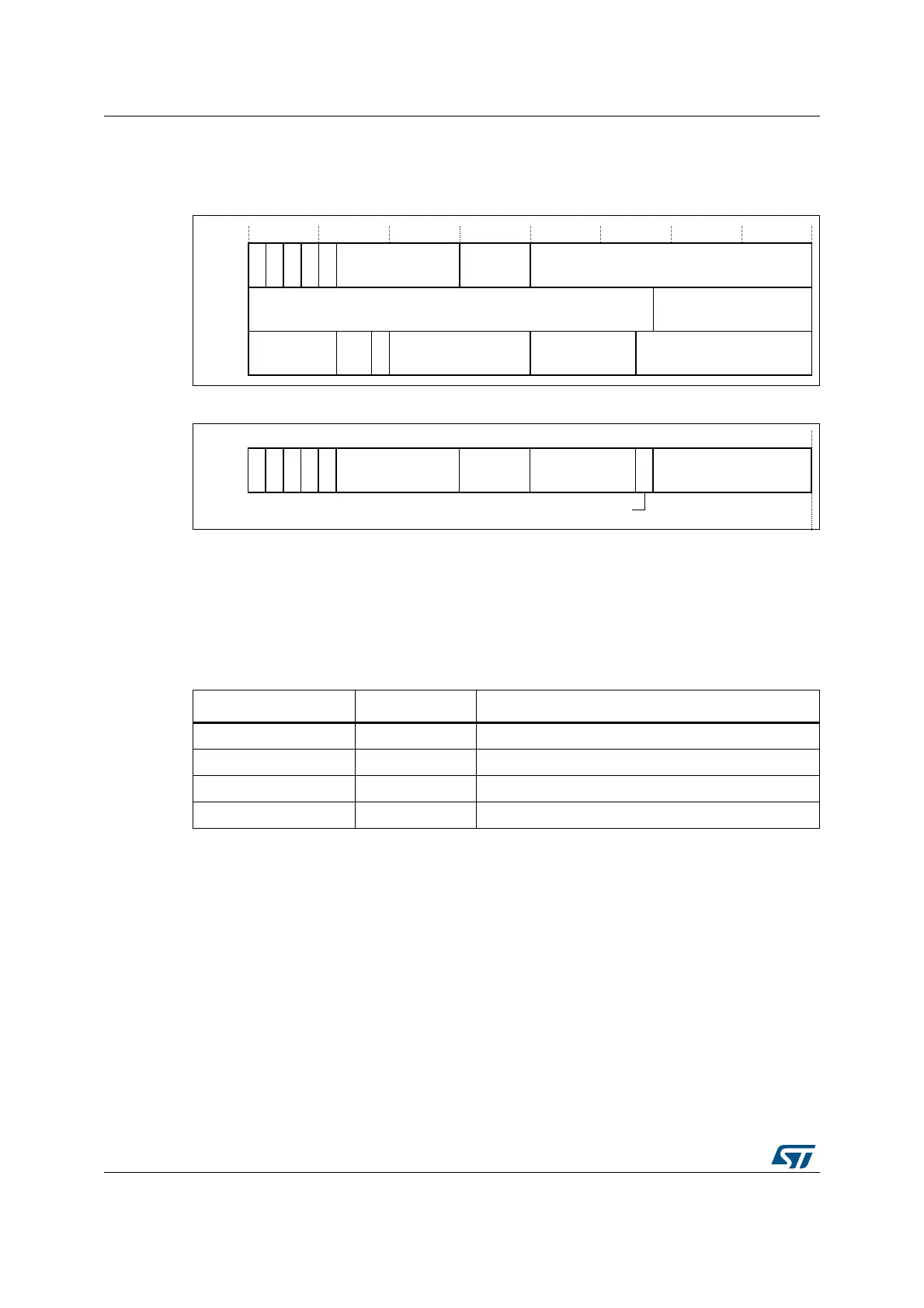

These registers are mutually exclusive bitfields in the 32-bit PSR. The bit assignment is

shown in Figure 3 and Figure 4.

Figure 3. APSR, IPSR and EPSR bit assignment

Figure 4. PSR bit assignment

Access these registers individually or as a combination of any two or all three registers,

using the register name as an argument to the MSR or MRS instructions. For example:

• Read all of the registers using PSR with the MRS instruction.

• Write to the APSR N, Z, C, V, and Q bits using APSR_nzcvq with the MSR instruction.

The PSR combinations and attributes are:

See the instruction descriptions MRS on page 186 and MSR on page 187 for more

information about how to access the program status registers.

Table 4. PSR register combinations

Register Type Combination

PSR read-write

(1), (2)

1. The processor ignores writes to the IPSR bits.

2. Reads of the EPSR bits return zero, and the processor ignores writes to the these bits

APSR, EPSR, and IPSR

IEPSR read-only EPSR and IPSR

IAPSR read-write

(1)

APSR and IPSR

EAPSR read-write

(2)

APSR and EPSR

5HVHUYHG ,65B180%(5

1=&9

5HVHUYHG

$365

,365

(365

5HVHUYHG 5HVHUYHG

5HVHUYHG,&,,7 ,&,,77

4

*(>@5HVHUYHG

1=&9

365

5HVHUYHG

,&,,7

4

*(>@5HVHUYHG

,65B180%(5

Loading...

Loading...