PM0214 Rev 9 19/262

PM0214 The Cortex-M4 processor

261

General-purpose registers

R0-R12 are 32-bit general-purpose registers for data operations.

Stack pointer

The Stack Pointer (SP) is register R13. In Thread mode, bit[1] of the CONTROL register

indicates the stack pointer to use:

• 0: Main Stack Pointer (MSP). This is the reset value.

• 1: Process Stack Pointer (PSP).

On reset, the processor loads the MSP with the value from address 0x00000000.

Link register

The Link Register (LR) is register R14. It stores the return information for subroutines,

function calls, and exceptions. On reset, the processor loads the LR value 0xFFFFFFFF.

Program counter

The Program Counter (PC) is register R15. It contains the current program address. On

reset, the processor loads the PC with the value of the reset vector, which is at address

0x00000004. Bit[0] of the value is loaded into the EPSR T-bit at reset and must be 1.

Program status register

The Program Status Register (PSR) combines:

• Application Program Status Register (APSR)

• Interrupt Program Status Register (IPSR)

• Execution Program Status Register (EPSR)

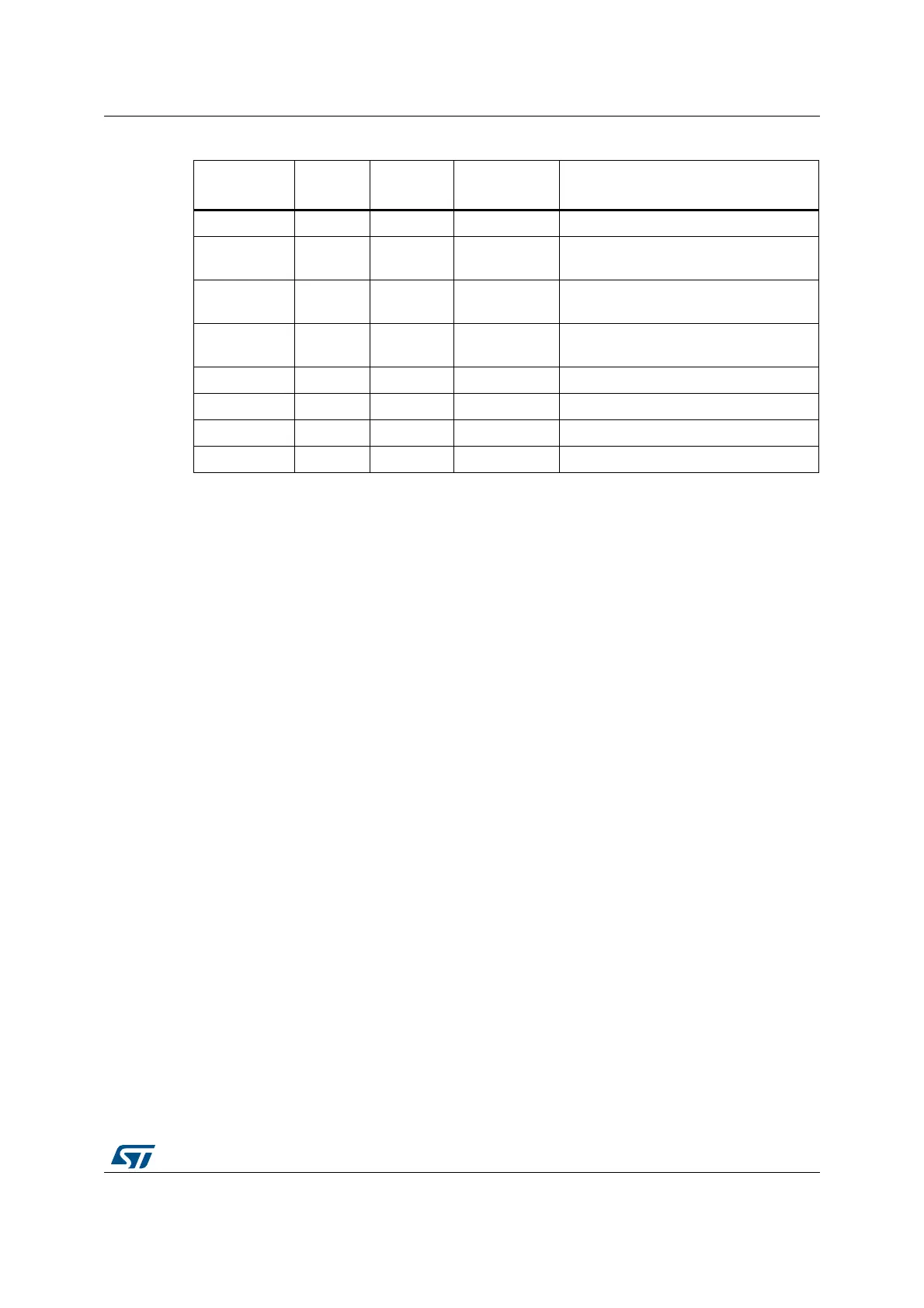

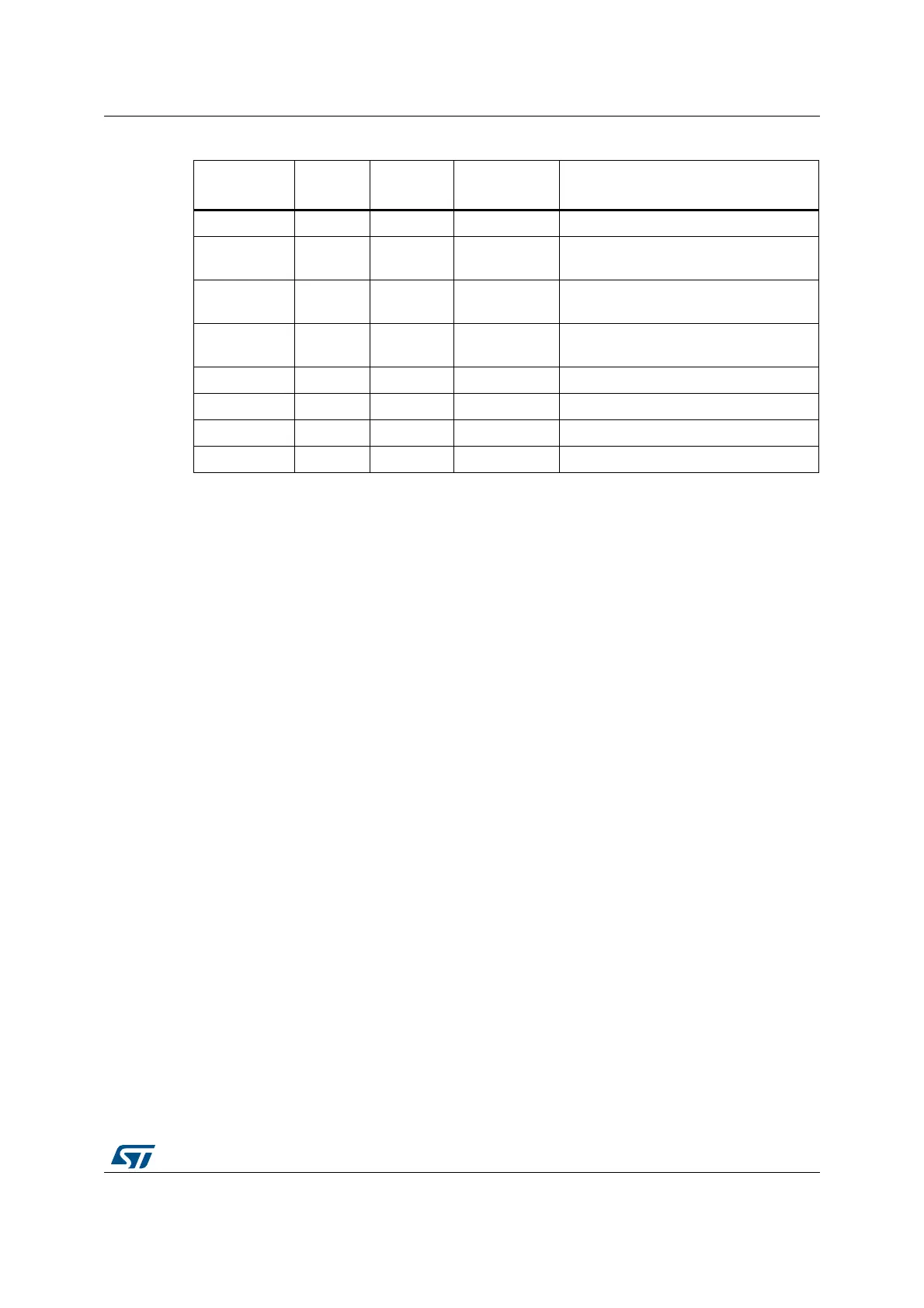

PSR read-write Privileged 0x01000000 Program status register on page 19

ASPR read-write Either Unknown

Application program status register on

page 21

IPSR read-only Privileged 0x00000000

Interrupt program status register on

page 22

EPSR read-only Privileged 0x01000000

Execution program status register on

page 22

PRIMASK read-write Privileged 0x00000000 Priority mask register on page 24

FAULTMASK read-write Privileged 0x00000000 Fault mask register on page 24

BASEPRI read-write Privileged 0x00000000 Base priority mask register on page 25

CONTROL read-write Privileged 0x00000000 CONTROL register on page 25

1. Describes access type during program execution in thread mode and Handler mode. Debug access can

differ.

2. An entry of either means privileged and unprivileged software can access the register.

Table 3. Core register set summary (continued)

Name Type

(1)

Required

privilege

(2)

Reset

value

Description

Loading...

Loading...