PM0214 Rev 9 235/262

PM0214 Core peripherals

261

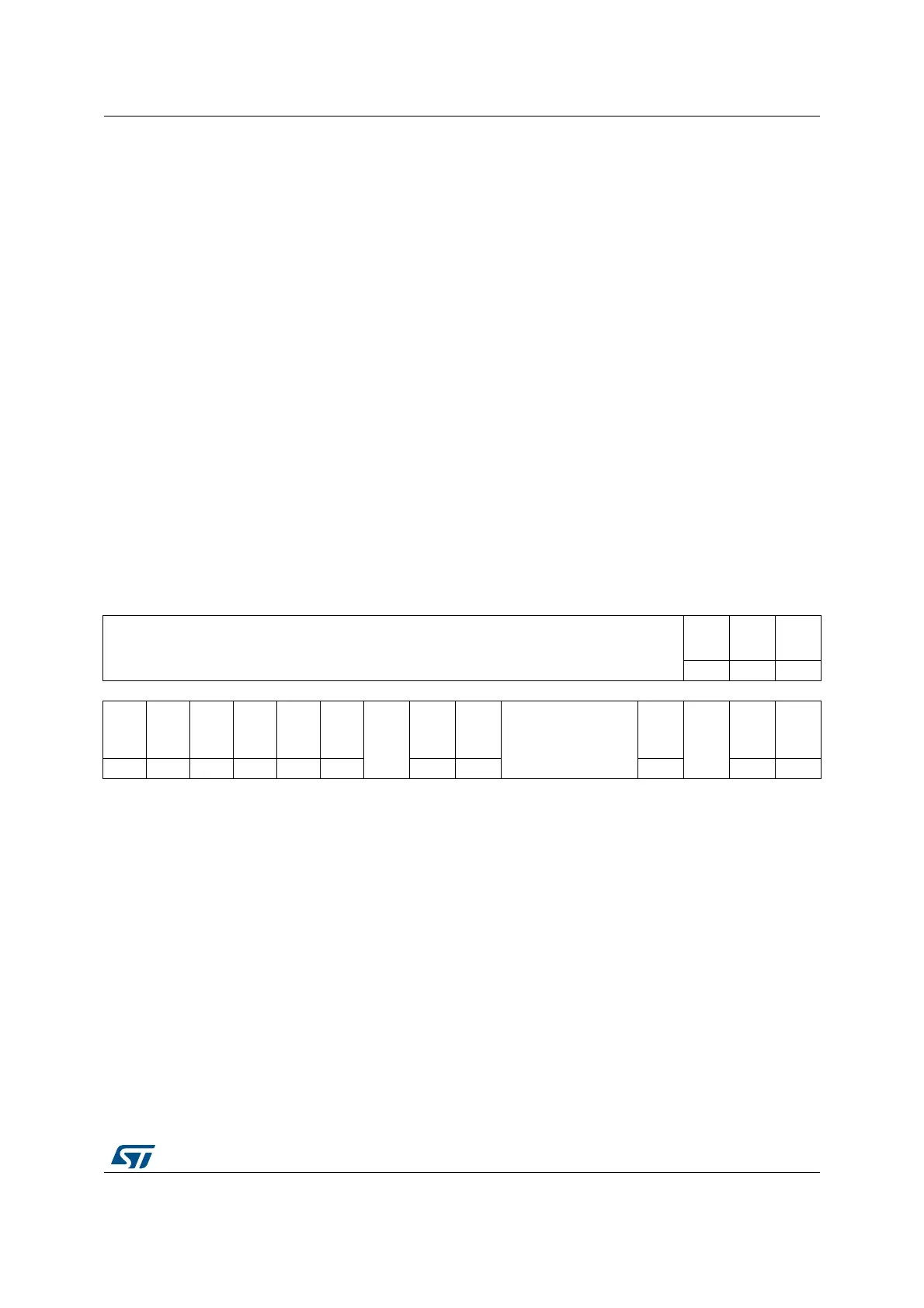

4.4.9 System handler control and state register (SHCSR)

Address offset: 0x24

Reset value: 0x0000 0000

Required privilege: Privileged

The SHCSR enables the system handlers, and indicates:

• The pending status of the bus fault, memory management fault, and SVC exceptions

• The active status of the system handlers.

If you disable a system handler and the corresponding fault occurs, the processor treats the

fault as a hard fault.

You can write to this register to change the pending or active status of system exceptions.

An OS kernel can write to the active bits to perform a context switch that changes the

current exception type.

• Software that changes the value of an active bit in this register without correct

adjustment to the stacked content can cause the processor to generate a fault

exception. Ensure software that writes to this register retains and subsequently

restores the current active status.

• After you have enabled the system handlers, if you have to change the value of a bit in

this register you must use a read-modify-write procedure to ensure that you change

only the required bit.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

USG

FAULT

ENA

BUS

FAULT

ENA

MEM

FAULT

ENA

rw rw rw

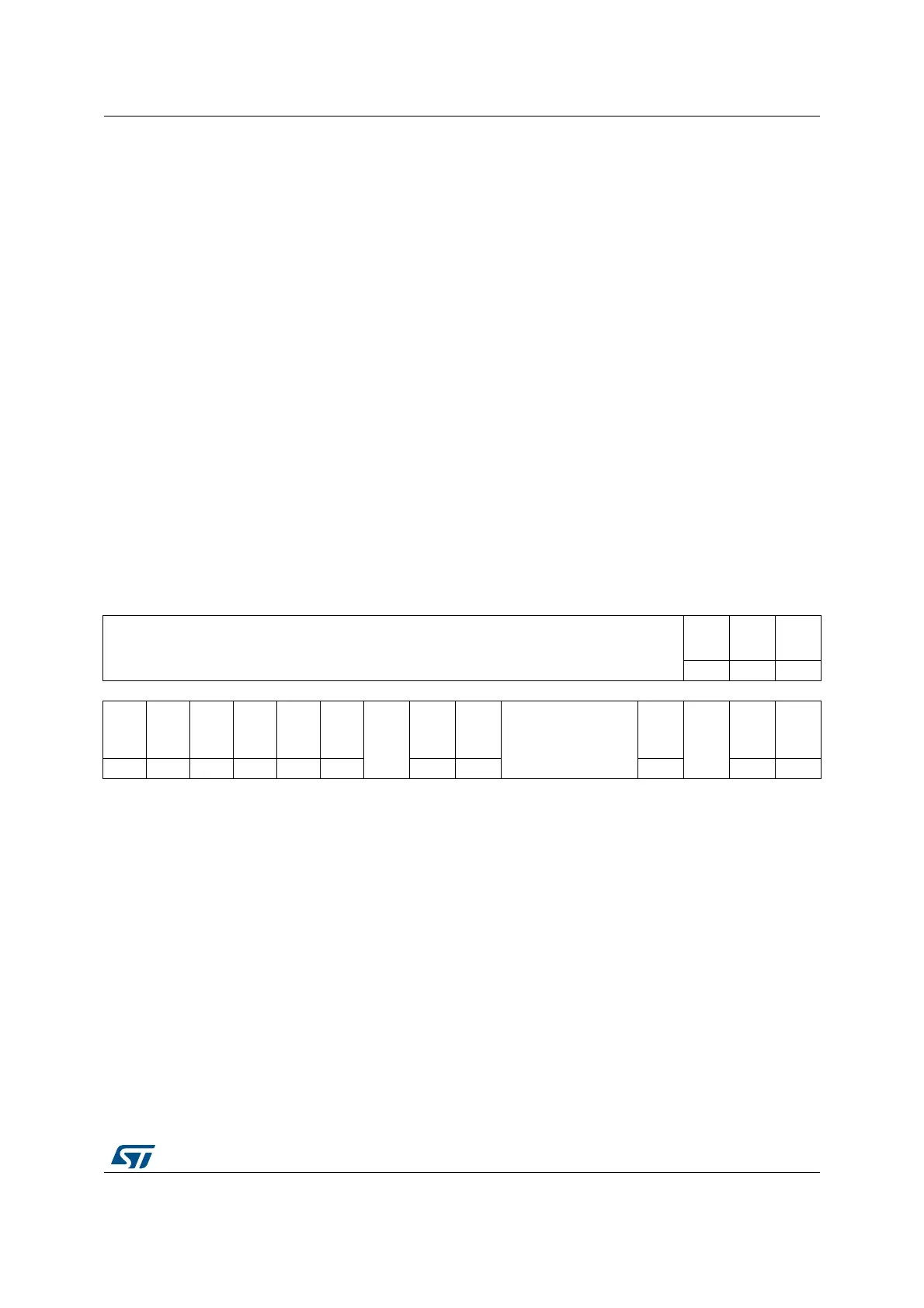

1514131211109876543210

SV

CALL

PEND

ED

BUS

FAULT

PEND

ED

MEM

FAULT

PEND

ED

USG

FAULT

PEND

ED

SYS

TICK

ACT

PEND

SV

ACT

Res.

MONIT

OR

ACT

SV

CALL

ACT

Reserved

USG

FAULT

ACT

Res.

BUS

FAULT

ACT

MEM

FAULT

ACT

rw rw rw rw rw rw rw rw rw rw rw

Bits 31:19 Reserved, must be kept cleared

Bit 18 USGFAULTENA: Usage fault enable bit, set to 1 to enable

(1)

Bit 17 BUSFAULTENA: Bus fault enable bit, set to 1 to enable

(1)

Bit 16 MEMFAULTENA: Memory management fault enable bit, set to 1 to enable

(1)

Bit 15 SVCALLPENDED: SVC call pending bit, reads as 1 if exception is pending

(2)

Bit 14 BUSFAULTPENDED: Bus fault exception pending bit, reads as 1 if exception is pending

(2)

Bit 13 MEMFAULTPENDED: Memory management fault exception pending bit, reads as 1 if

exception is pending

(2)

Bit 12 USGFAULTPENDED: Usage fault exception pending bit, reads as 1 if exception is pending

(2)

Bit 11 SYSTICKACT: SysTick exception active bit, reads as 1 if exception is active

(3)

Bit 10 PENDSVACT: PendSV exception active bit, reads as 1 if exception is active

Bit 9

Reserved, must be kept cleared

Loading...

Loading...