Core peripherals PM0214

252/262 PM0214 Rev 9

4.6 Floating point unit (FPU)

The Cortex-M4F FPU implements the FPv4-SP floating-point extension.

The FPU fully supports single-precision add, subtract, multiply, divide, multiply and

accumulate, and square root operations. It also provides conversions between fixed xxxxx-

point and floating-point data formats, and floating-point constant instructions.

The FPU provides floating-point computation functionality that is compliant with the

ANSI/IEEE standard 754-2008, IEEE standard for Binary Floating-Point Arithmetic, referred

to as the IEEE 754 standard.

The FPU contains 32 single-precision extension registers, which you can also access as 16

doubleword registers for load, store, and move operations.

Table 56 shows the floating-point system registers in the Cortex-M4F system control block

(SCB). The base address of the additional registers for the FP extension is 0xE000 ED00.

The following sections describe the floating-point system registers whose implementation is

specific to this processor.

Note: For more details on the IEEE standard and floating-point arithmetic (IEEE 754), refer to the

AN4044 Application note. Available from website www.st.com.

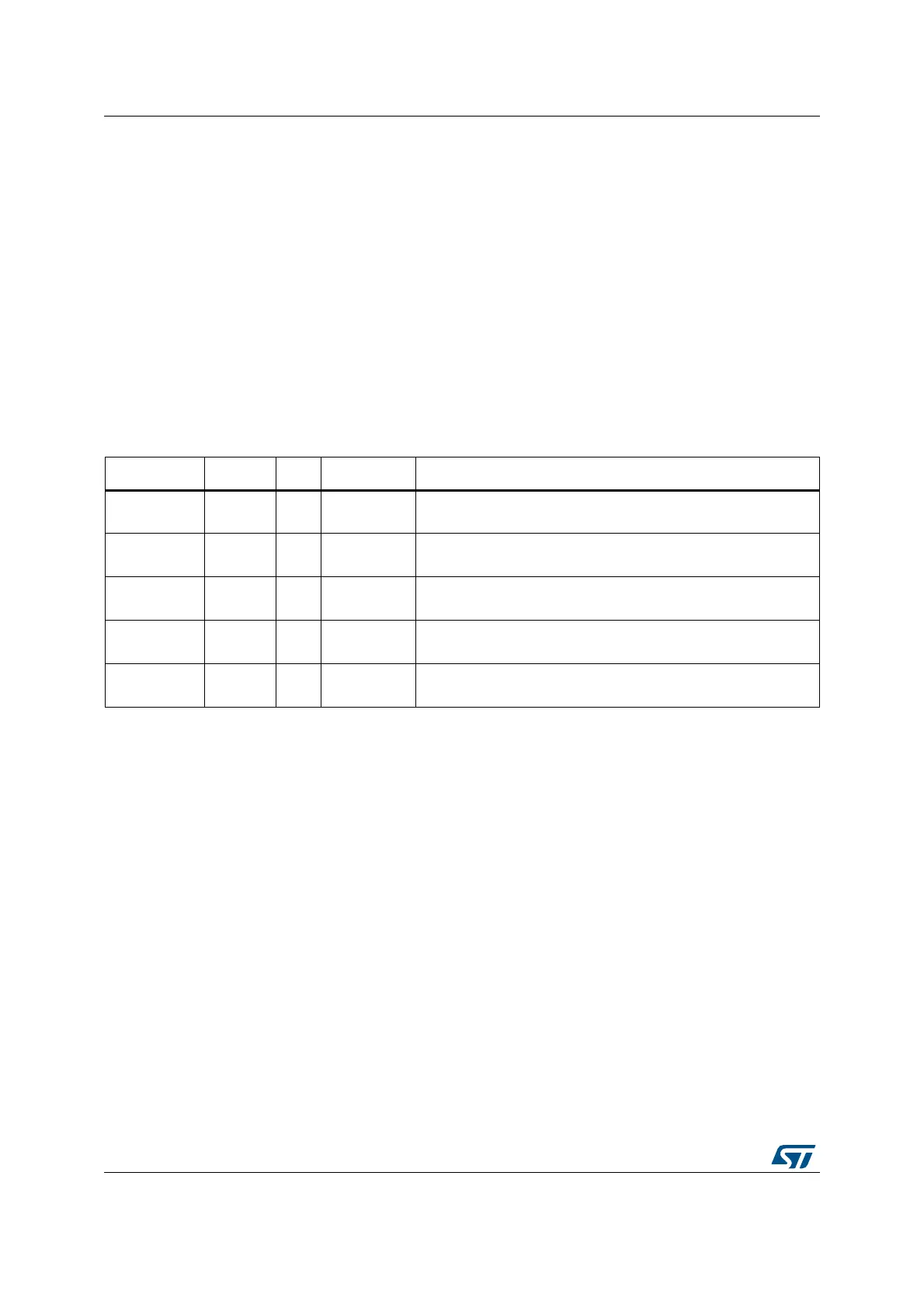

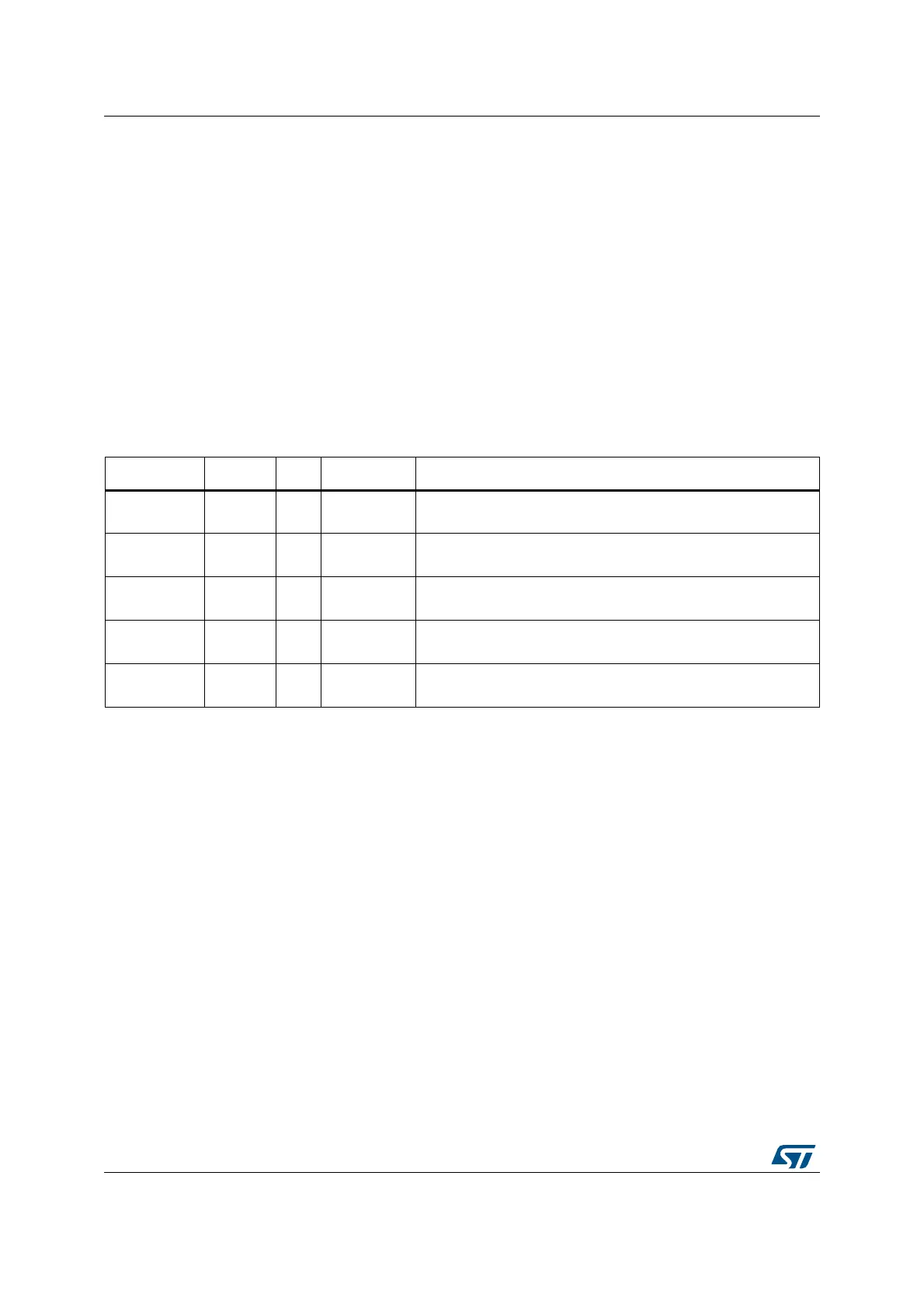

Table 56. Cortex-M4F floating-point system registers

Address Name Type Reset Description

0xE000ED88 CPACR RW 0x00000000

Section 4.6.1: Coprocessor access control register (CPACR) on

page 253

0xE000EF34 FPCCR RW 0xC0000000

Section 4.6.2: Floating-point context control register (FPCCR)

on page 253

0xE000EF38 FPCAR RW -

Section 4.6.3: Floating-point context address register (FPCAR)

on page 255

0xE000EF3C FPDSCR RW 0x00000000

Section 4.6.5: Floating-point default status control register

(FPDSCR) on page 257

- FPSCR RW -

Section 4.6.4: Floating-point status control register (FPSCR) on

page 255

Loading...

Loading...