PM0214 Rev 9 45/262

PM0214 The Cortex-M4 processor

261

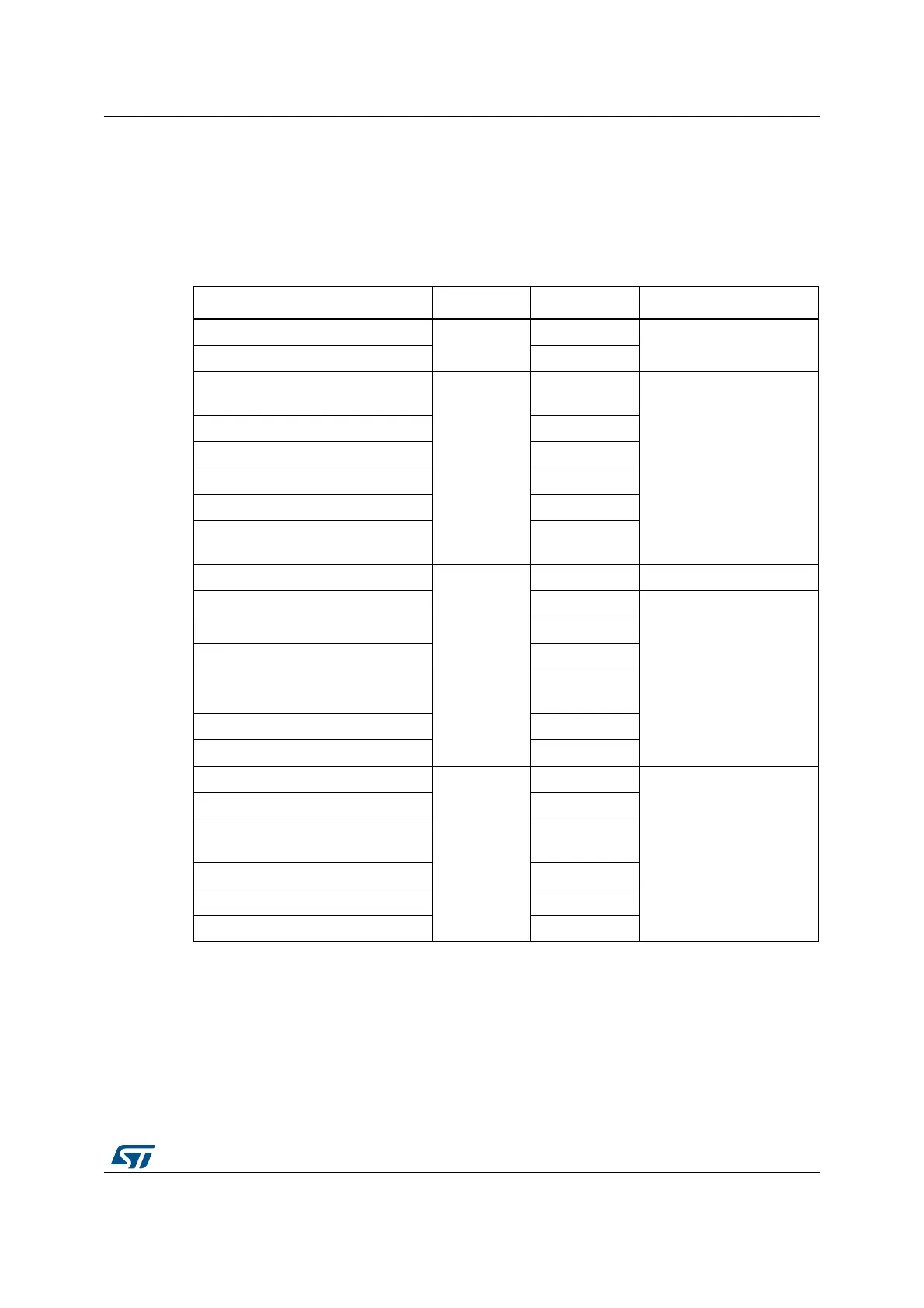

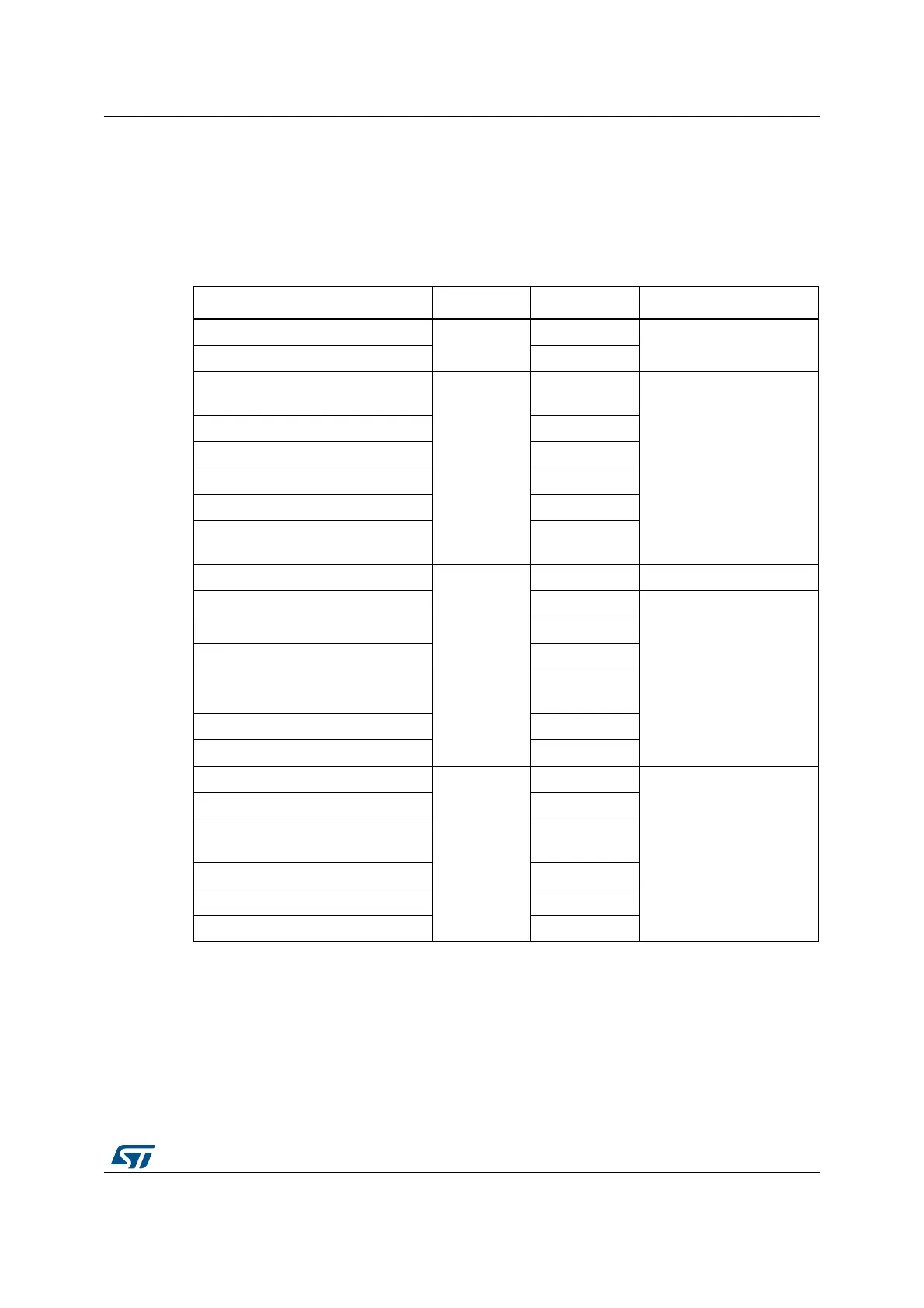

2.4.1 Fault types

Table 19 shows the types of fault, the handler used for the fault, the corresponding fault

status register, and the register bit that indicates that the fault has occurred. See

Configurable fault status register (CFSR; UFSR+BFSR+MMFSR) on page 237 for more

information about the fault status registers.

Table 19. Faults

Fault Handler Bit name Fault status register

Bus error on a vector read

Hard fault

VECTTBL

Hard fault status register

(HFSR) on page 241

Fault escalated to a hard fault FORCED

MPU or default memory map

mismatch:

MemManage

-

Memory management fault

address register (MMFAR)

on page 242

– on instruction access IACCVIOL

(1)

1. Occurs on an access to an XN region even if the MPU is disabled.

– on data access DACCVIOL

– during exception stacking MSTKERR

– during exception unstacking MUNSKERR

– during lazy floating-point state

preservation

MLSPERR

Bus error:

Bus fault

--

– During exception stacking STKERR

Bus fault address register

(BFAR) on page 242

– During exception unstacking UNSTKERR

– During instruction prefetch IBUSERR

– During lazy floating-point state

preservation

LSPERR

Precise data bus error PRECISERR

Imprecise data bus error IMPRECISERR

Attempt to access a coprocessor

Usage fault

NOCP

Configurable fault status

register (CFSR;

UFSR+BFSR+MMFSR) on

page 237

Undefined instruction UNDEFINSTR

Attempt to enter an invalid instruction

set state

(2)

2. Attempting to use an instruction set other than the Thumb instruction set, or returns to a non load/store-

multiple instruction with ICI continuation.

INVSTATE

Invalid EXC_RETURN value INVPC

Illegal unaligned load or store UNALIGNED

Divide By 0 DIVBYZERO

Loading...

Loading...