PM0214 Rev 9 81/262

PM0214 The STM32 Cortex-M4 instruction set

261

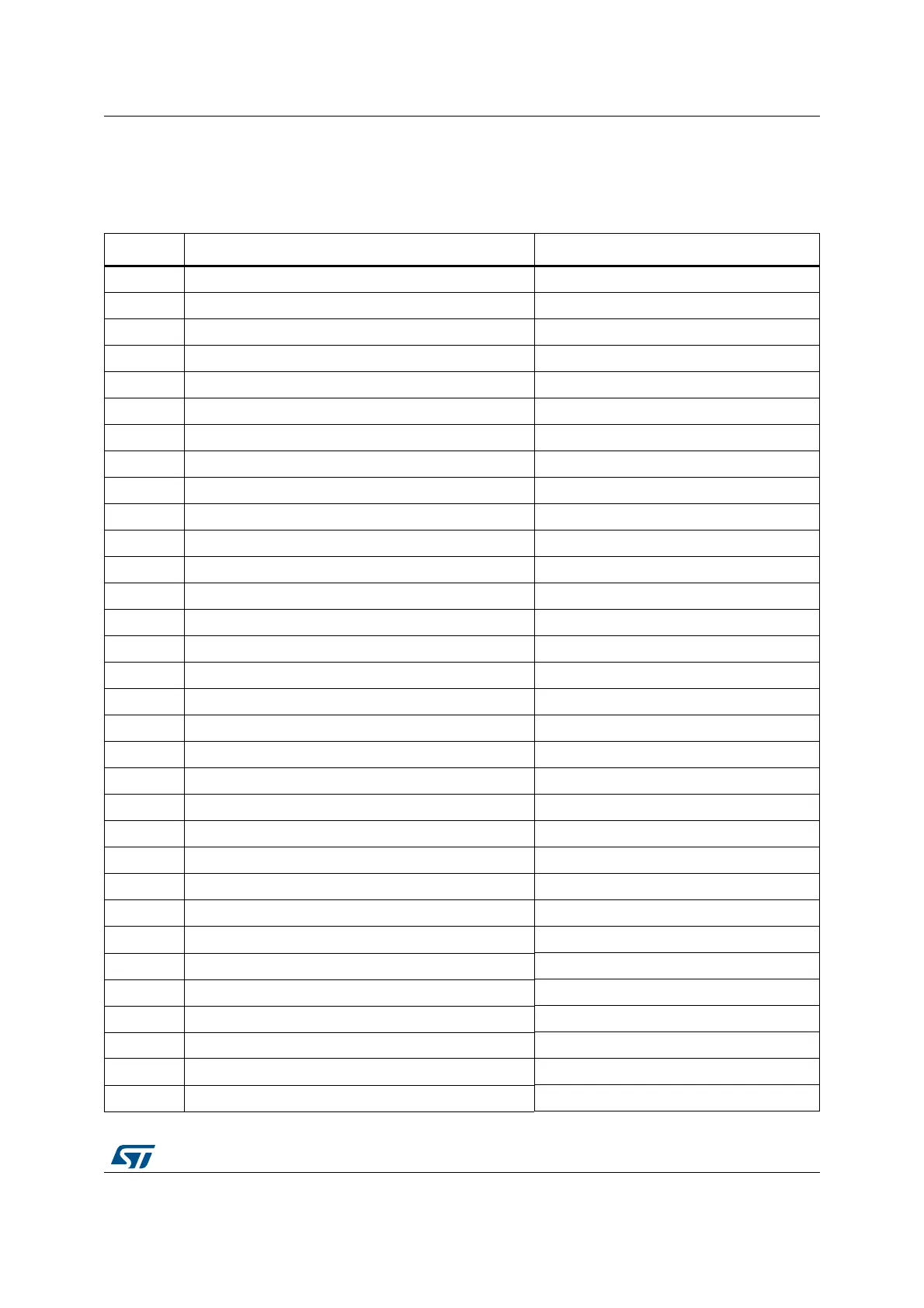

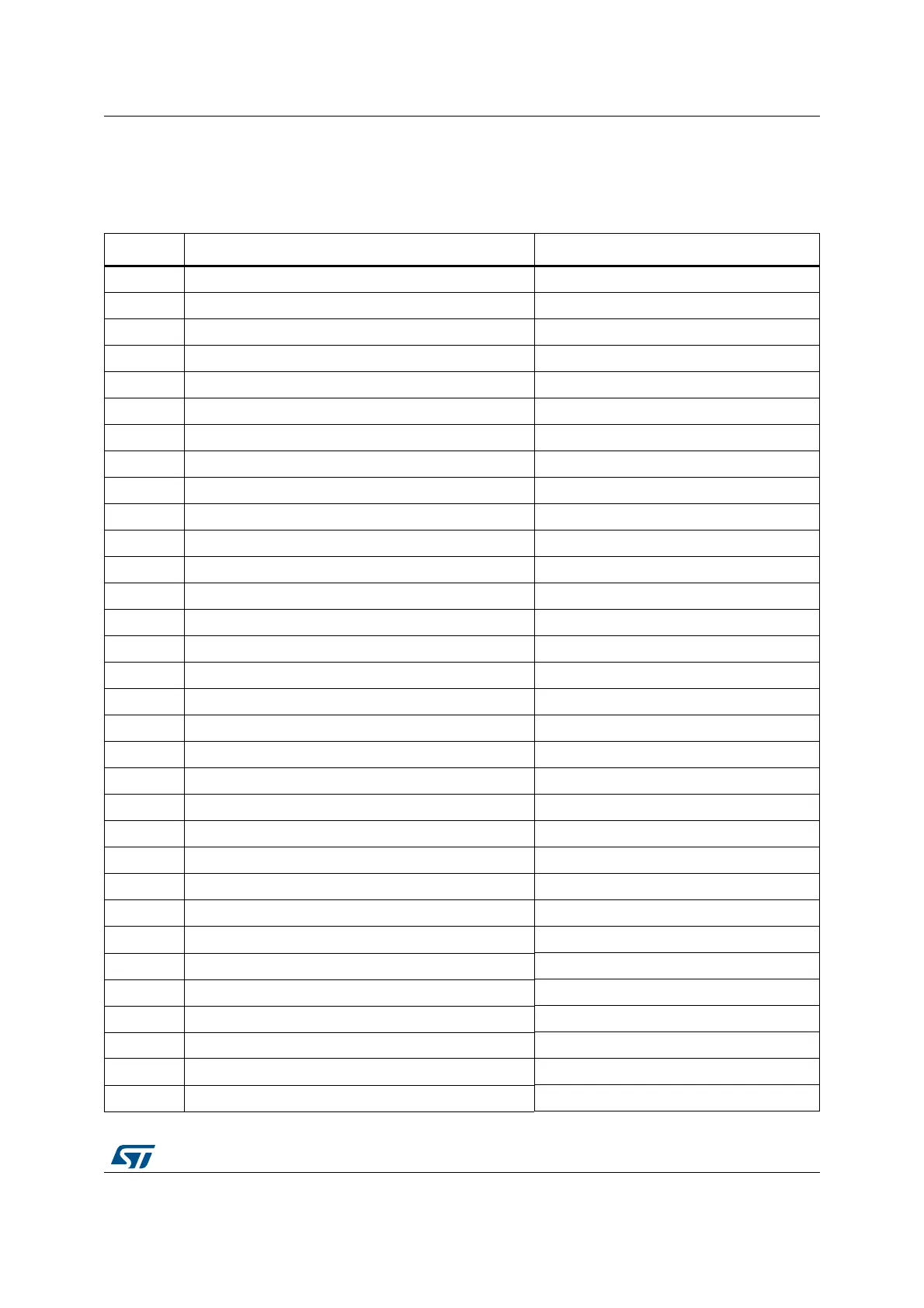

3.5 General data processing instructions

Table 28 shows the data processing instructions.

Table 28. Data processing instructions

Mnemonic Brief description See

ADC Add with carry ADD, ADC, SUB, SBC, and RSB on page 83

ADD Add ADD, ADC, SUB, SBC, and RSB on page 83

ADDW Add ADD, ADC, SUB, SBC, and RSB on page 83

AND Logical AND AND, ORR, EOR, BIC, and ORN on page 85

ASR Arithmetic Shift Right ASR, LSL, LSR, ROR, and RRX on page 86

BIC Bit Clear AND, ORR, EOR, BIC, and ORN on page 85

CLZ Count leading zeros CLZ on page 87

CMN Compare Negative CMP and CMN on page 88

CMP Compare CMP and CMN on page 88

EOR Exclusive OR AND, ORR, EOR, BIC, and ORN on page 85

LSL Logical Shift Left ASR, LSL, LSR, ROR, and RRX on page 86

LSR Logical Shift Right ASR, LSL, LSR, ROR, and RRX on page 86

MOV Move MOV and MVN on page 89

MOVT Move Top MOVT on page 91

MOVW Move 16-bit constant MOV and MVN on page 89

MVN Move NOT MOV and MVN on page 89

ORN Logical OR NOT AND, ORR, EOR, BIC, and ORN on page 85

ORR Logical OR AND, ORR, EOR, BIC, and ORN on page 85

RBIT Reverse Bits REV, REV16, REVSH, and RBIT on page 92

REV Reverse byte order in a word REV, REV16, REVSH, and RBIT on page 92

REV16 Reverse byte order in each halfword REV, REV16, REVSH, and RBIT on page 92

REVSH Reverse byte order in bottom halfword and sign extend REV, REV16, REVSH, and RBIT on page 92

ROR Rotate Right ASR, LSL, LSR, ROR, and RRX on page 86

RRX Rotate Right with Extend ASR, LSL, LSR, ROR, and RRX on page 86

RSB Reverse Subtract ADD, ADC, SUB, SBC, and RSB on page 83

SADD16 Signed Add 16 SADD16 and SADD8 on page 93

SADD8 Signed Add 8 SADD16 and SADD8 on page 93

SASX Signed Add and Subtract with Exchange SASX and SSAX on page 98

SSAX Signed Subtract and Add with Exchange SASX and SSAX on page 98

SBC Subtract with Carry ADD, ADC, SUB, SBC, and RSB on page 83

SHADD16 Signed Halving Add 16 SHADD16 and SHADD8 on page 94

SHADD8 Signed Halving Add 8 SHADD16 and SHADD8 on page 94

Loading...

Loading...