Sun Microelectronics

123

7. UltraSPARC External Interfaces

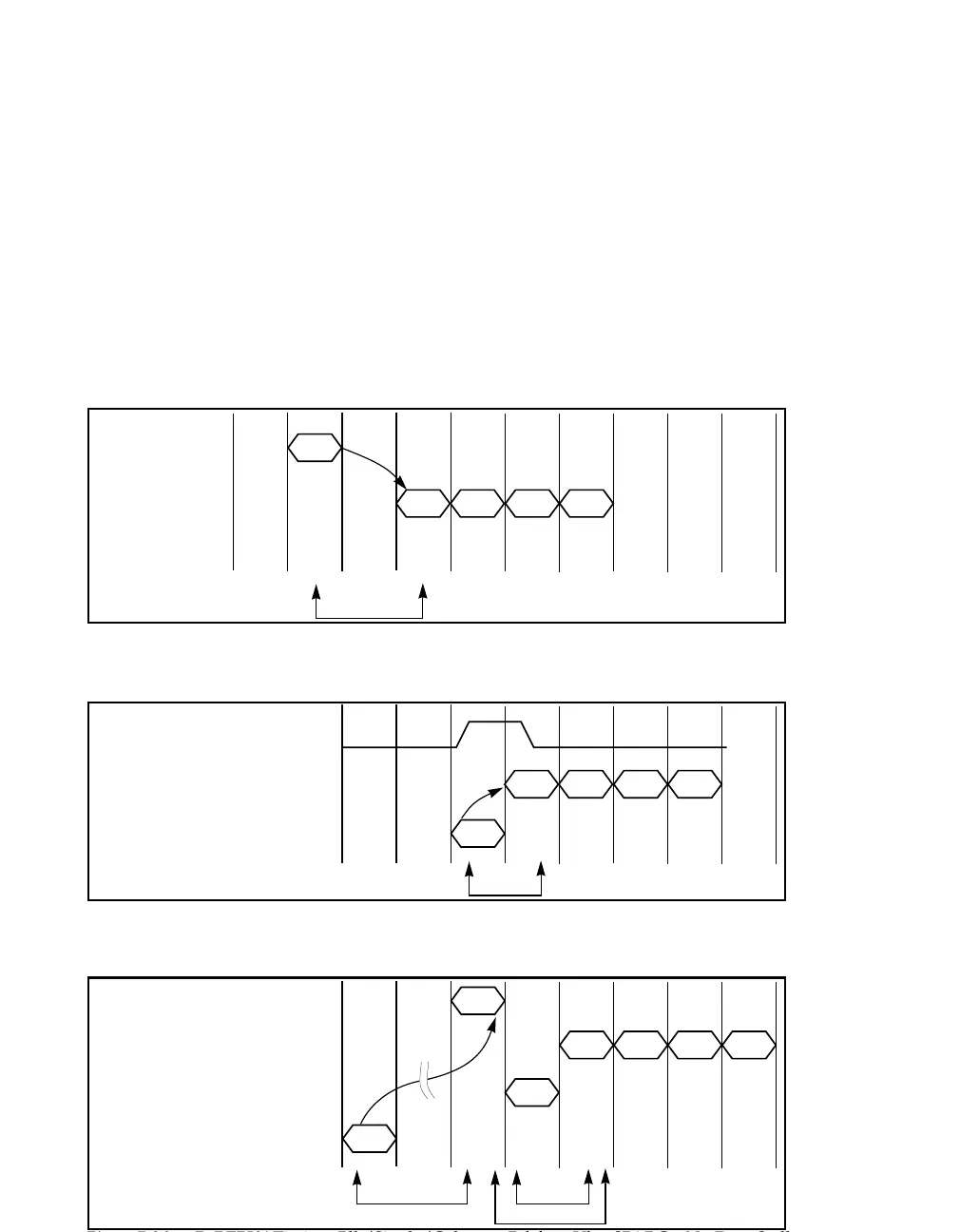

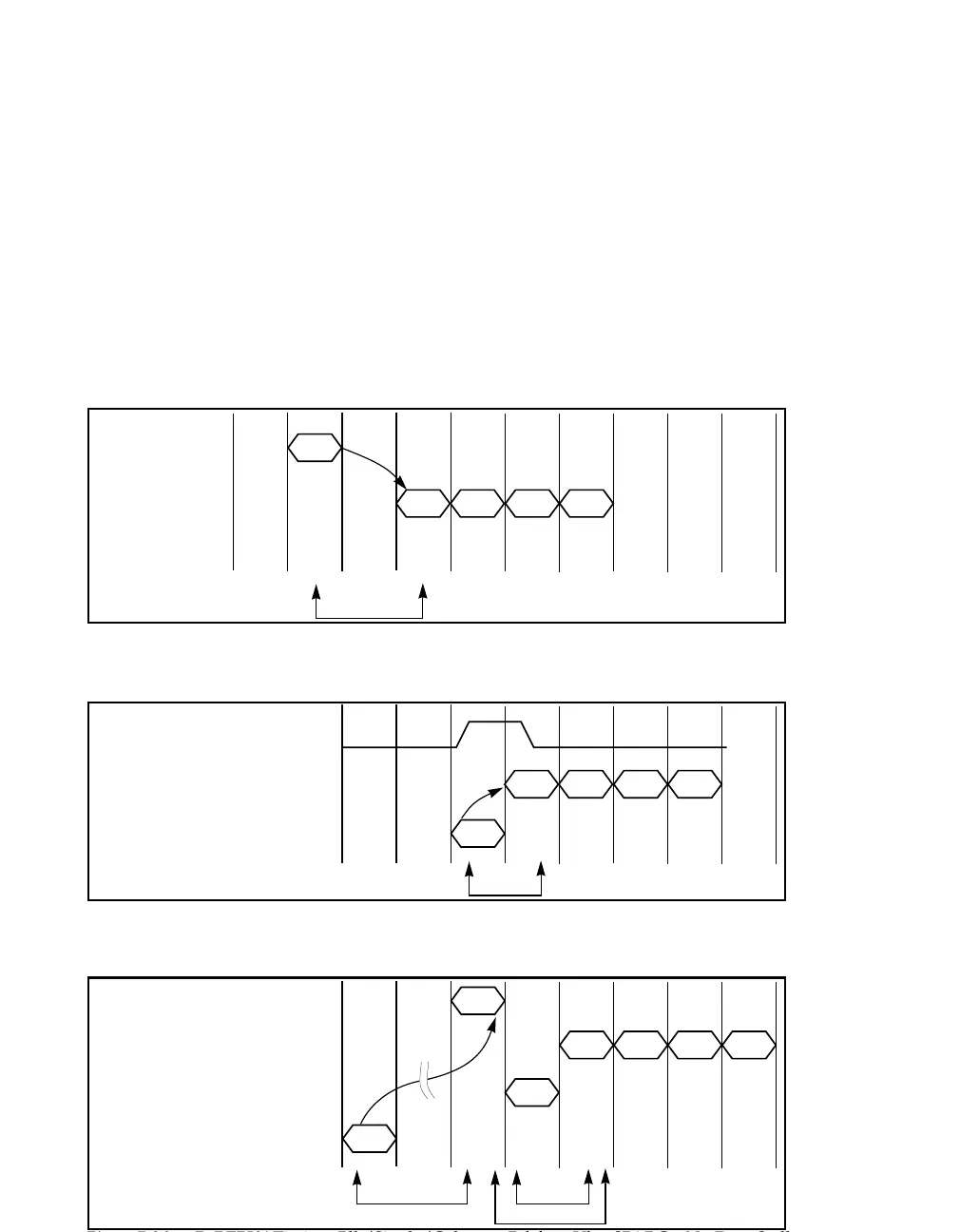

7.13.3 P_REPLY and S_REPLY Timing

The following figures show the data flow on SYSDATA due to S_REPLY and

P_REPLY with no data stalls. Figure 7-25 also shows the timing of the

interconnect_ECC_Valid signal with respect to the S_REPLY. Section 7.13.4 dis-

cusses data flow timing with data stalls.

Figure 7-24 S_REPLY Timing: UltraSPARC Sourcing Block Write—No Data Stall

Figure 7-25 S_REPLY Timing: UltraSPARC Receiving Block Write—No Data Stall

Figure 7-26 P_REPLY Timing: Blk/Single/Coherent Rd fromUltraSPARC—No Data Stall

S_REPLY

Data on Bus

S_WAB

D[0] D[1] D[2] D[3]

2 clocks

S_REPLY to Data Sink

Data on Bus

S_SWB

D[0] D[1] D[2] D[3]

1 clock

interconnect_ECC_Valid

S_REPLY to Data Sink

Data on Bus

S_SWB

D[0] D[1] D[2] D[3]

1 clock

S_REPLY to Data Source

P_REPLY from Slave

P_RAS

S_SRS

min 2 clocks

2 clocks

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...