Sun Microelectronics

124

UltraSPARC User’s Manual

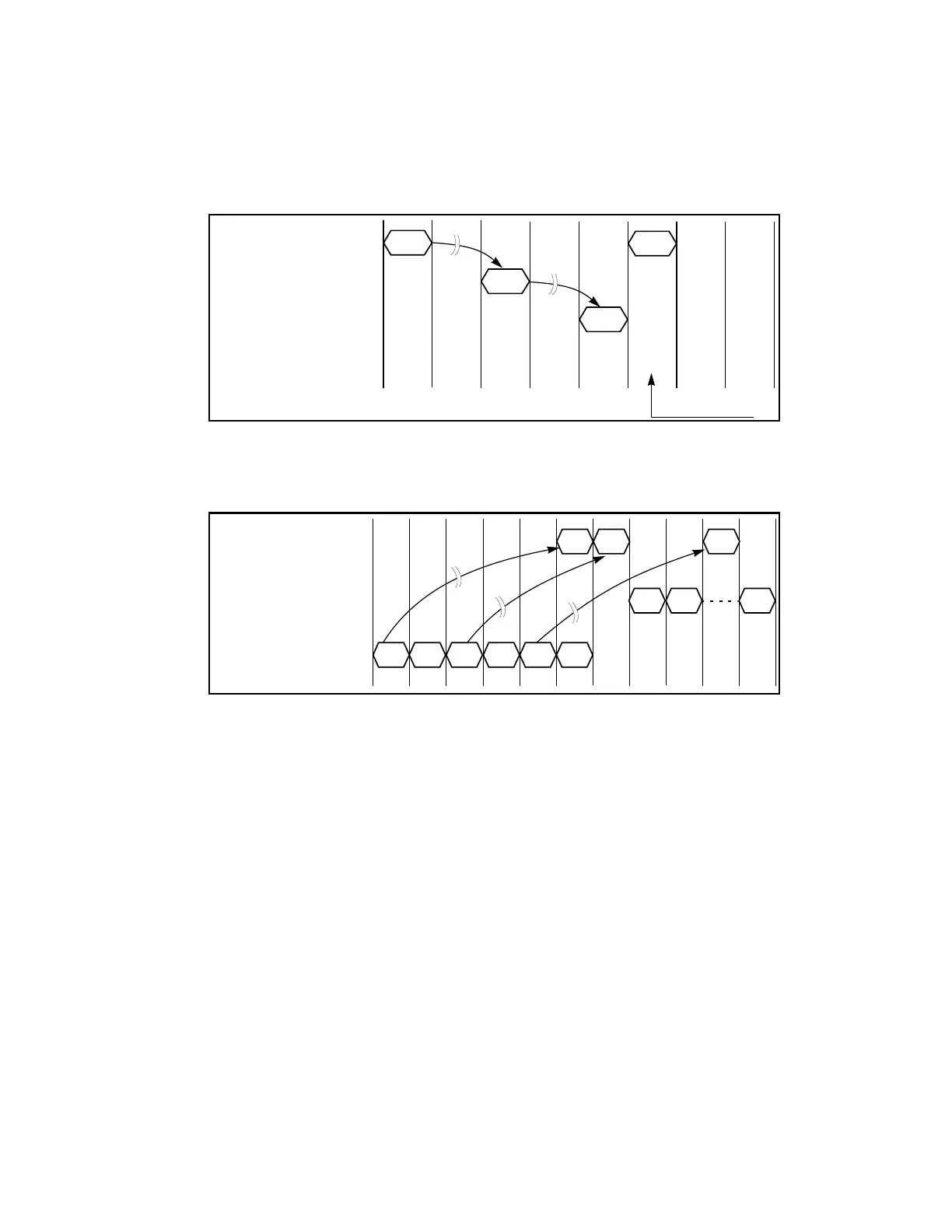

Figure 7-27 Back-to-Back Coherent S_REQs to UltraSPARC

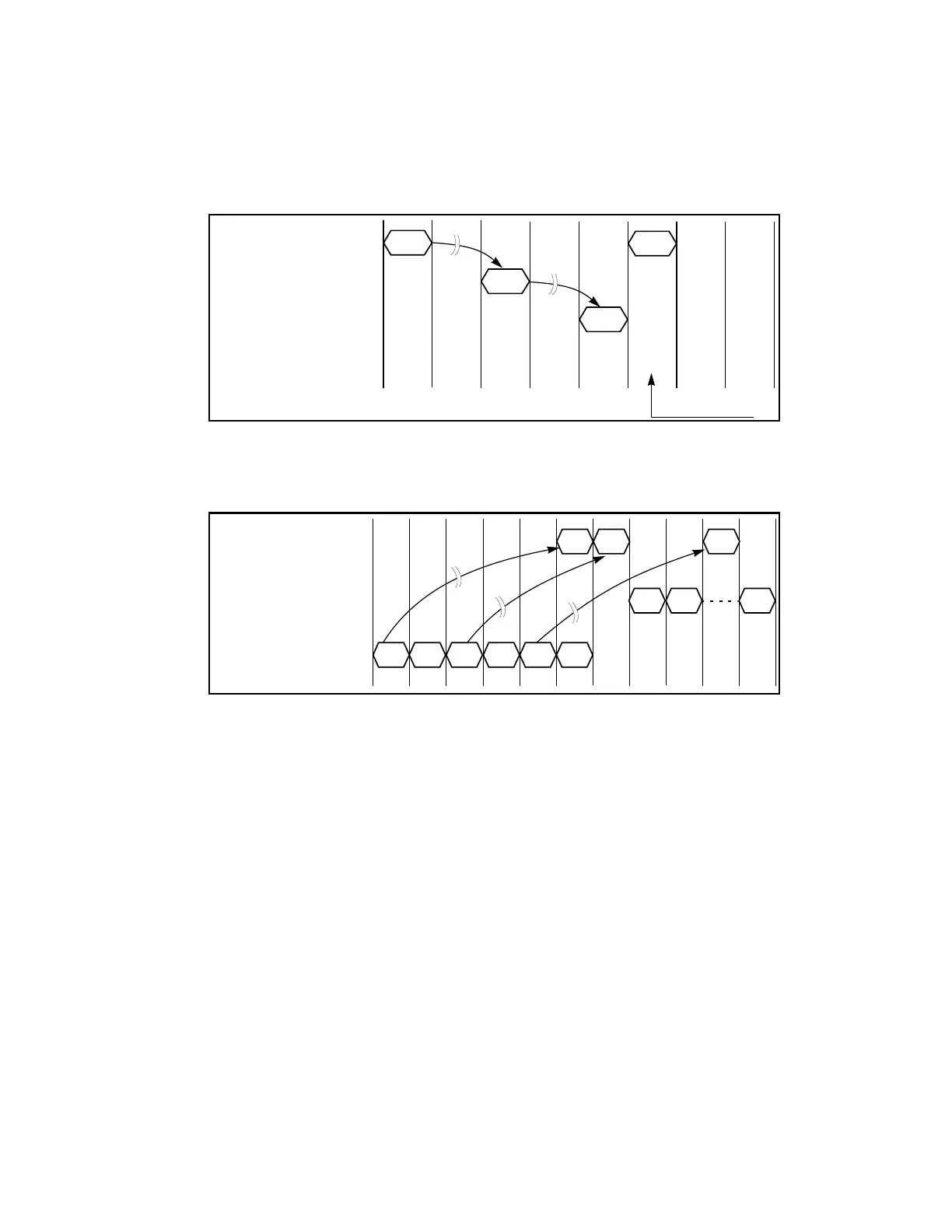

Figure 7-28 S_REPLY Pipelining to UltraSPARC for Data Transfers

7.13.4 Data Stall

Normally, each 128-bit data word of a 64-byte block transfer flows on SYSDATA

in successive clock cycles without stalls. To facilitate flexible timings for DRAMs,

however, a Data_Stall signal is provided to allow the SC to delay individual

128-bit transfers. Data_Stall also qualifies the S_REPLY signal accompanying a

data transfer. The following rules govern the assertion of Data_Stall:

1. When UltraSPARC is sourcing data, the earliest that SC can assert

Data_Stall is one system clock cycle after it asserts S_REPLY. Asserting

Data_Stall causes the data being driven on SYSDATA during the following

system clock to be held for an additional clock.

S_REPLY to Get Data

P_REPLY

S_REQ

S_REQ

Earliest S_REQ2

S_REQ2

P_SACK

S_CRAB

NCWR1

S_REPLY to UltraSPARC

P_REQ from UltraSPARC

Data on Bus

NCWR1 NCWR2 NCWR2 RDS3 RDS3

S_WAS S_WAS2 S_RBU3

D[1] D[2] D[3]

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...