Sun Microelectronics

137

7. UltraSPARC External Interfaces

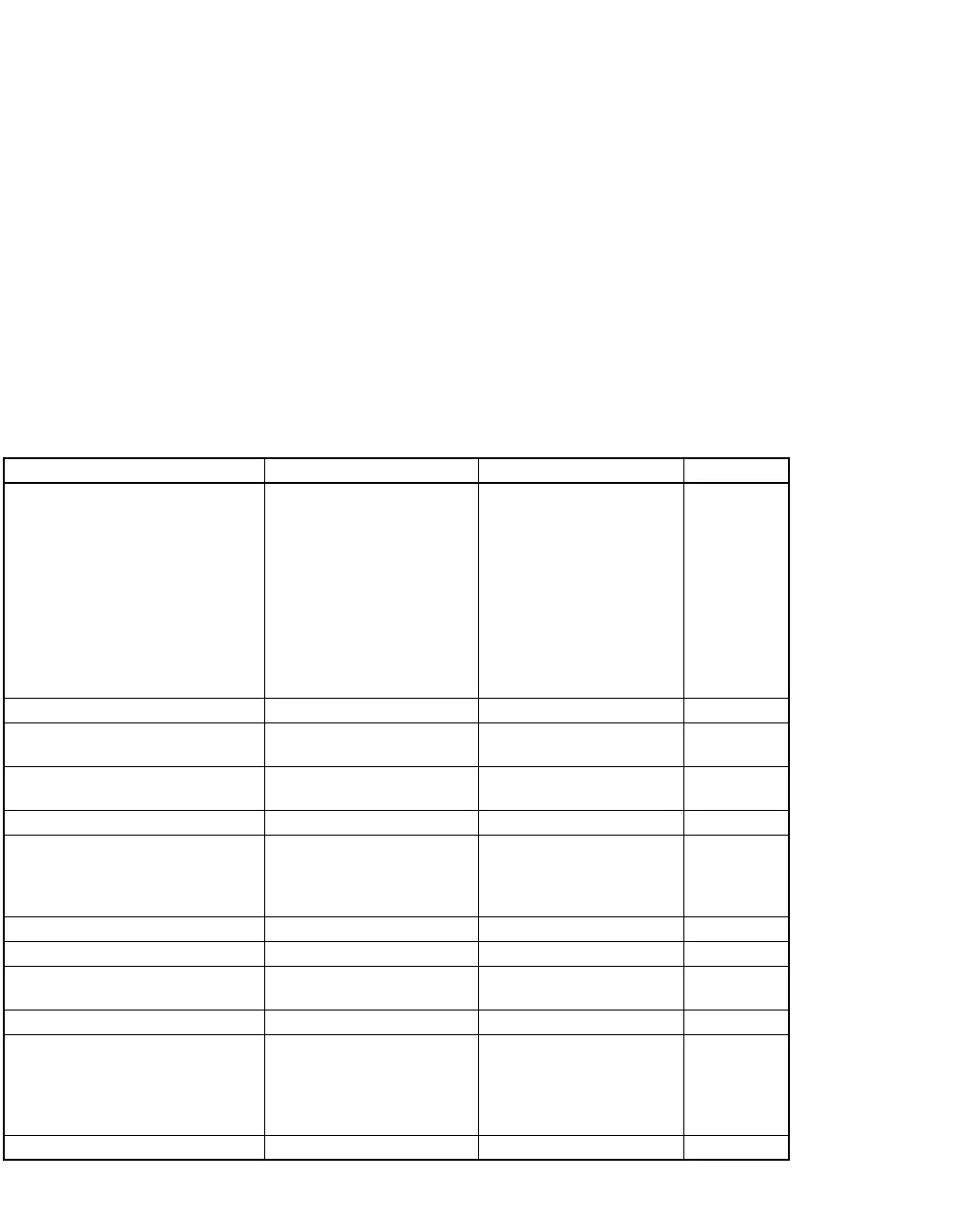

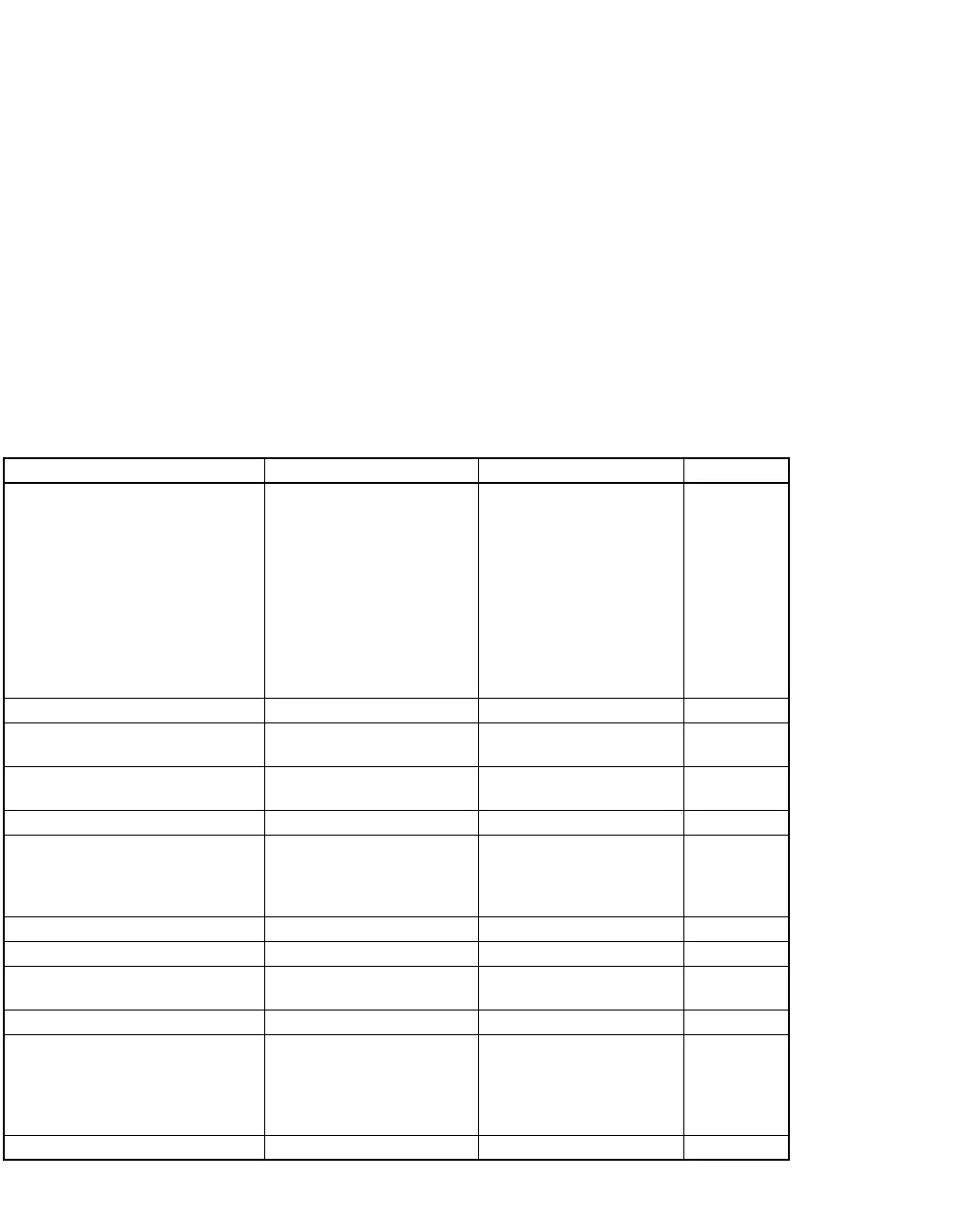

7.16.11 ReadToOwn Dirty Victimized Block

Condition: Store miss by another processor (P2).

The transaction sequence shown in Table 7-35 is the same as in Section 7.16.8,

“Victim Writeback,” except that another processor P2 makes a ReadToOwn re-

quest for the victimized block in P1 before the Writeback transaction from P1 has

been acknowledged by System.

Table 7-35 Copyback-Invalidate Dirty Victimized Block

Processor 1 System Processor 2 Processor 3

Initial victim state:

Etag1{M}

Initial missed state:

Etag2{I}

P1 copies the victimized block into

the writeback buffer}

P_RDS_REQ to System

(DVP bit set)

Initial state:

Etag1{I}

Initial state:

Etag2{I}

Initial state:

Etag2{I}

S_RBU reply to P1

P1 reads the data

updates Etag2{I → E}

P_RDO_REQ to System for

victim block in P1.

S_CPI_REQ to P1

P1 makes another copy of the victim

block in the copyback buffer

P_SACKD reply to System

S_CRAB reply to P1

S_RBU reply to P2

P2 reads data and updates

Etag1{I → M}

P_WRB_REQ to system

S_WBCAN to P1

(as the Writeback has been

cancelled due to the earlier

CPI request from System due

to P2’s RDO request)

P1 clears writeback buffer tag

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...