Sun Microelectronics

191

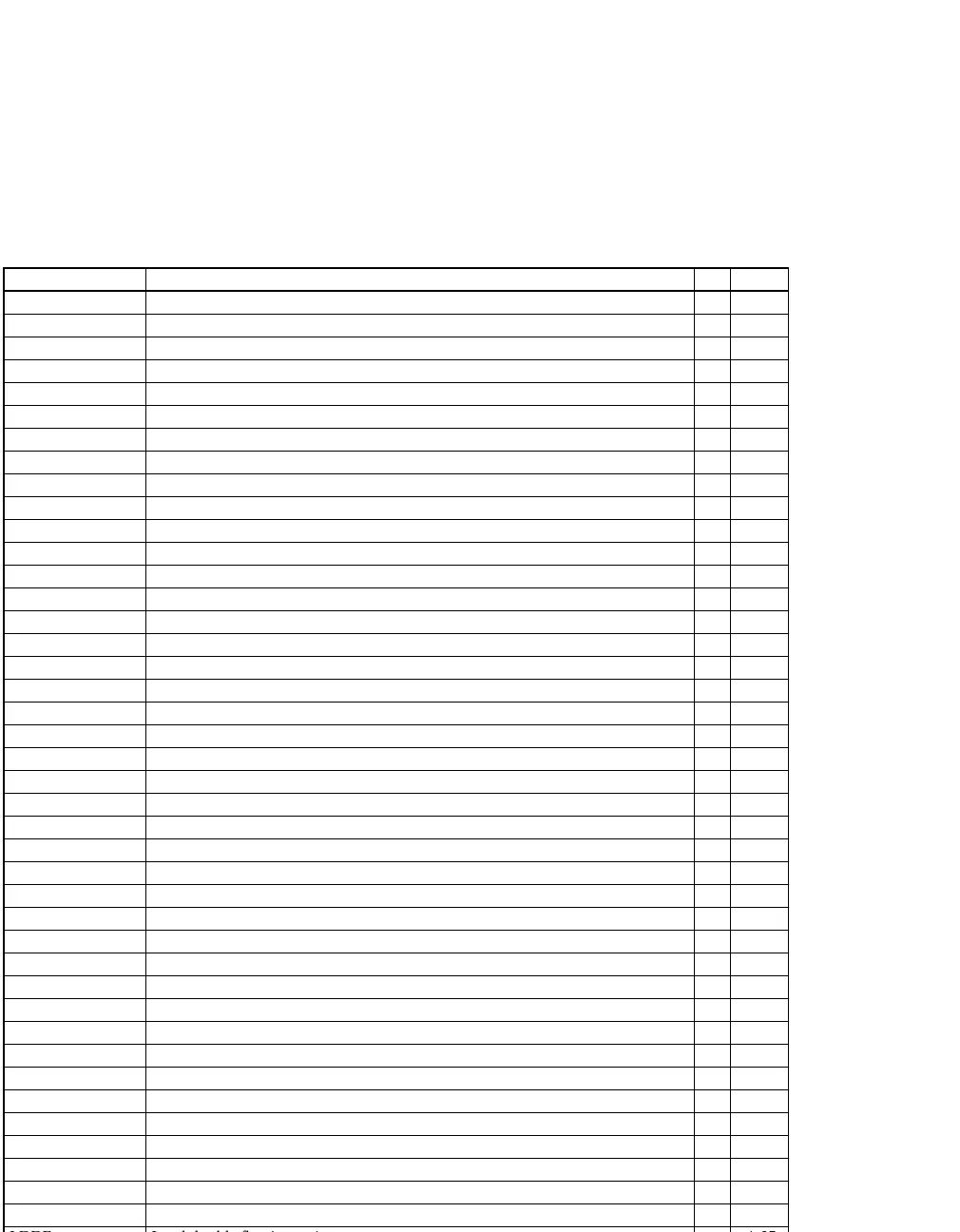

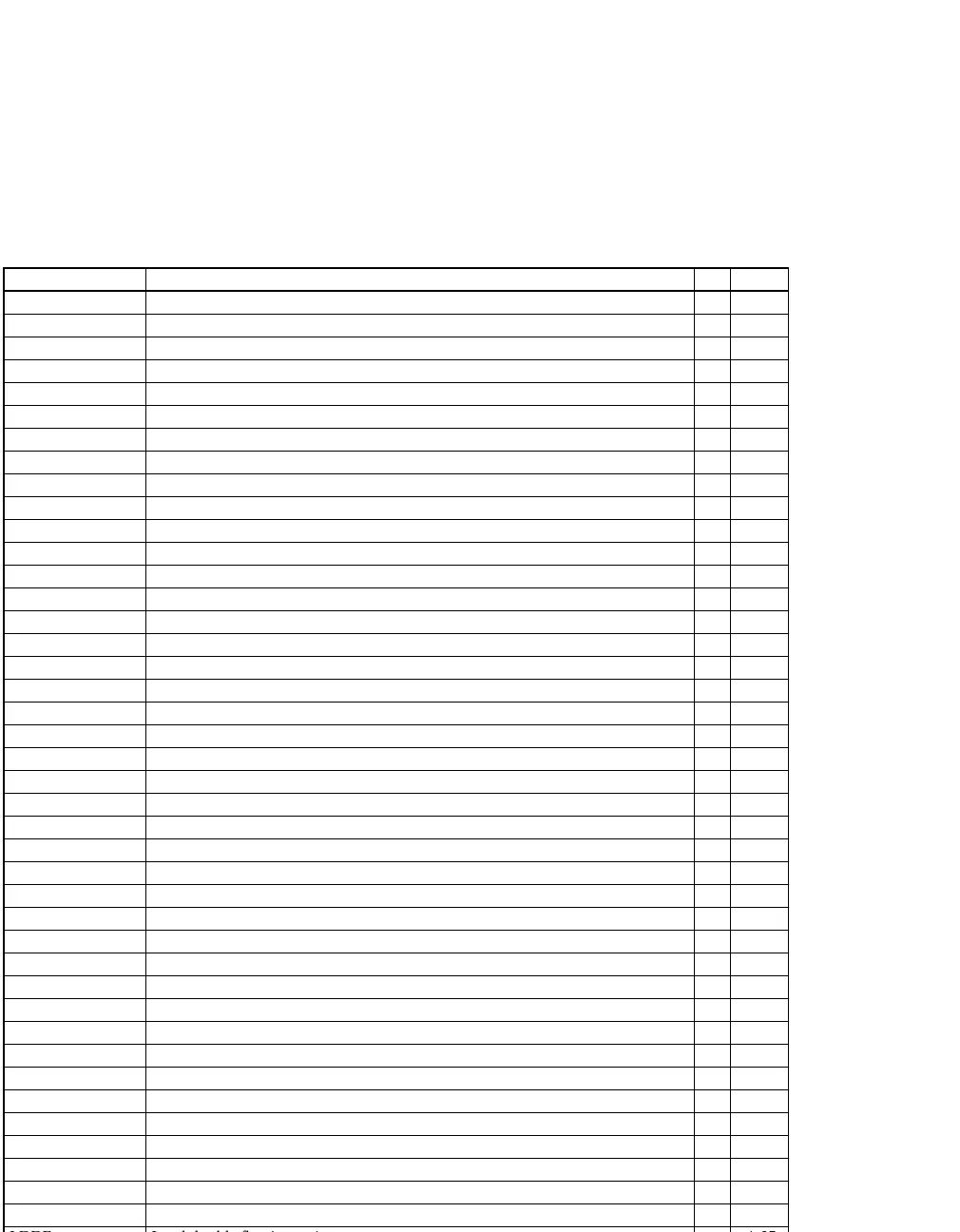

12. Instruction Set Summary

FMUL(s,d,q) Floating-point multiply A.18

FMUL8SUx16 Signed upper 8- × 16-bit partitioned product of corresponding components ✓ 13.5.4

FMUL8ULx16 Unsigned lower 8- × 16-bit partitioned product of corresponding components ✓ 13.5.4

FMUL8x16 8- × 16-bit partitioned product of corresponding components ✓ 13.5.4

FMUL8x16AL 8- × 16-bit lower α partitioned product of 4 components ✓ 13.5.4

FMUL8x16AU 8- × 16-bit upper α partitioned product of 4 components ✓ 13.5.4

FMULD8SUx16 Signed upper 8- × 16-bit multiply → 32-bit partitioned product of components ✓ 13.5.4

FMULD8ULx16 Unsigned lower 8- × 16-bit multiply → 32-bit partitioned product of components ✓ 13.5.4

FNAND{s} Logical NAND (single precision) ✓ 13.5.6

FNEG(s,d,q) Floating-point negate ✓ 13.5.6

FNOR{s} Logical NOR (single precision) ✓ 13.5.6

FNOT1{s} Negate (1’s complement) src1 (single precision) ✓ 13.5.6

FNOT2{s} Negate (1’s complement) src2 (single precision) ✓ 13.5.6

FONE{s} One fill(single precision) ✓ 13.5.6

FORNOT1{s} Negated src1 OR src2 (single precision) ✓ 13.5.6

FORNOT2{s} src1 OR negated src2 (single precision) ✓ 13.5.6

FOR{s} Logical OR (single precision) ✓ 13.5.6

FPACKFIX Two 32-bit to 16-bit fixed pack ✓ 13.5.3

FPACK{16,32} Four 16-bit/two 32-bit pixel pack ✓ 13.5.3

FPADD{16,32}{s} Four 16-bit/two 32-bit partitioned add (single precision) ✓ 13.5.2

FPMERGE Two 32-bit pixel to 64-bit pixel merge ✓ 13.5.3

FPSUB{16,32}{s} Four 16-bit/two 32-bit partitioned subtract (single precision) ✓ 13.5.2

FsMULd Floating-point multiply single to double A.18

FSQRT(s,d,q) Floating-point square root A.19

FSRC1{s} Copy src1 (single precision) ✓ 13.5.6

FSRC2{s} Copy src2 (single precision) ✓ 13.5.6

F(s,d,q)TO(s,d,q) Convert between floating-point formats A.15

F(s,d,q)TOi Convert floating point to integer A.14

F(s,d,q)TOx Convert floating point to 64-bit integer A.14

FSUB(s,d,q) Floating-point subtract A.12

FXNOR{s} Logical XNOR (single precision) ✓ 13.5.6

FXOR{s} Logical XOR (single precision) ✓ 13.5.6

FxTO(s,d,q) Convert 64-bit integer to floating-point A.16

FZERO{s} Zero fill(single precision) ✓ 13.5.6

ILLTRAP Illegal instruction A.22

IMPDEP1 Implementation-dependent instruction A.23

IMPDEP2 Implementation-dependent instruction A.23

JMPL Jump and link A.24

LDD Load doubleword A.27

LDDA Load doubleword from alternate space A.28

LDDA 128-bit atomic load ✓ 13.6.3

LDDF Load double floating-point A.25

Table 12-1 Complete UltraSPARC Instruction Set (Continued)

Opcode Description Ext Ref

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...