Sun Microelectronics

246

UltraSPARC User’s Manual

RD: IEEE Std 754-1985 Rounding Direction.

TEM: 5-bit trap enable mask for the IEEE-754 floating-point exceptions. If a

floating-point operate instruction produces one or more exceptions, the

corresponding cexc/aexc bits are set and an

fp_exception_ieee_754

(with

FSR.ftt=1,

IEEE_754_exception

) exception is generated.

NS: When this field = 0, UltraSPARC produces IEEE-754 compatible results.

In particular, subnormal operands or results may cause a trap. When this

field=1, UltraSPARC may deliver a non-IEEE-754 compatible result. In

particular, subnormal operands and results may be flushed to zero. See

Table 14-4, “Subnormal Operand Trapping Cases (NS=0),” on page 243

and Table 14-5, “Subnormal Result Trapping Cases (NS=0),” on page 243.

ver: This field identifies a particular implementation of the UltraSPARC FPU

architecture.

ftt: The 3-bit floating point trap type field is set whenever an floating-point

instruction causes the

fp_exception_ieee_754

or

fp_exception_other

traps.

Note: UltraSPARC neither detects nor generates the following trap types

directly in hardware:

hardware_error

,

invalid_fp_register

.

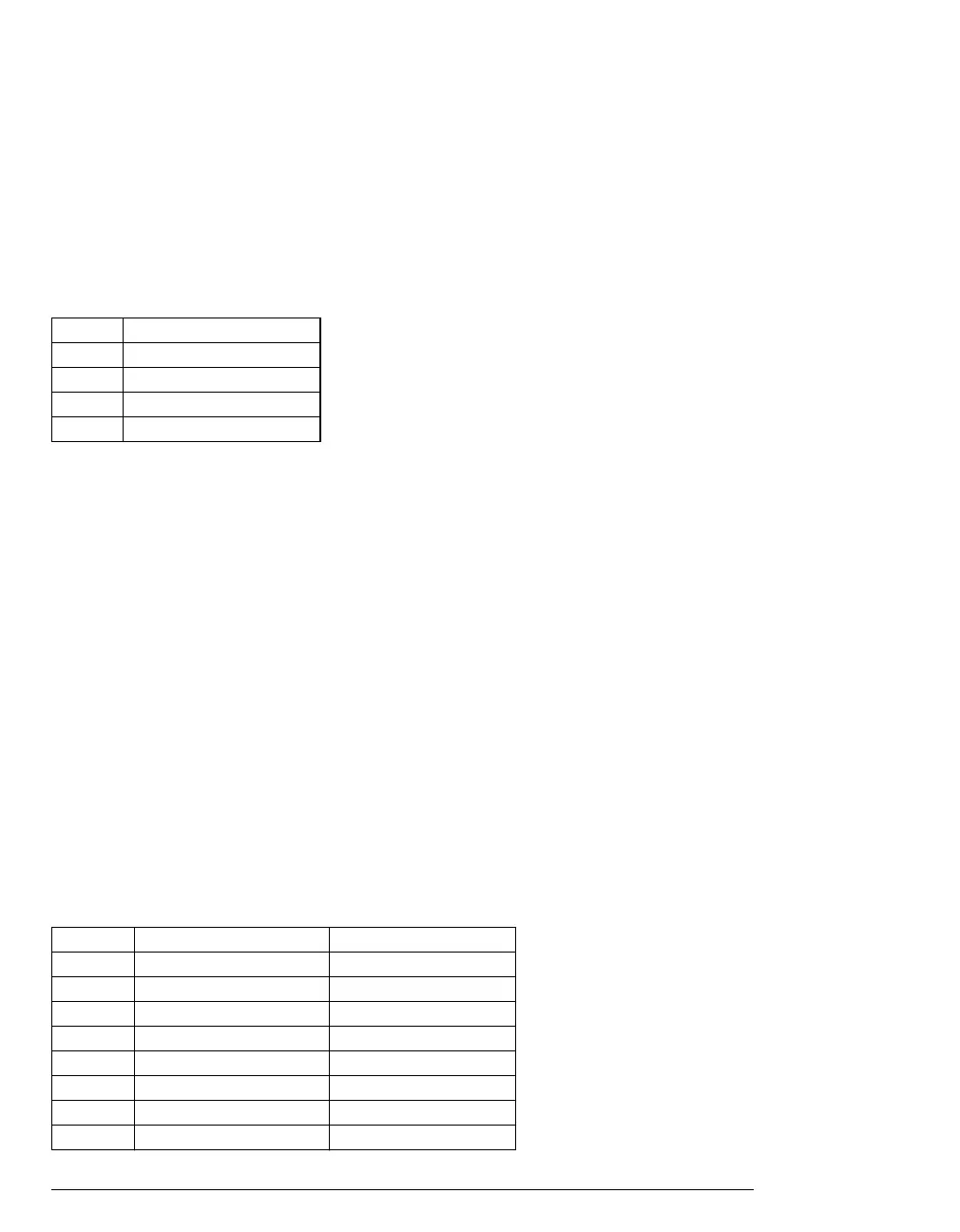

Table 14-8 Floating-Point Rounding Modes

RD Round Toward

0 Nearest (even if tie)

10

2+∞

3–∞

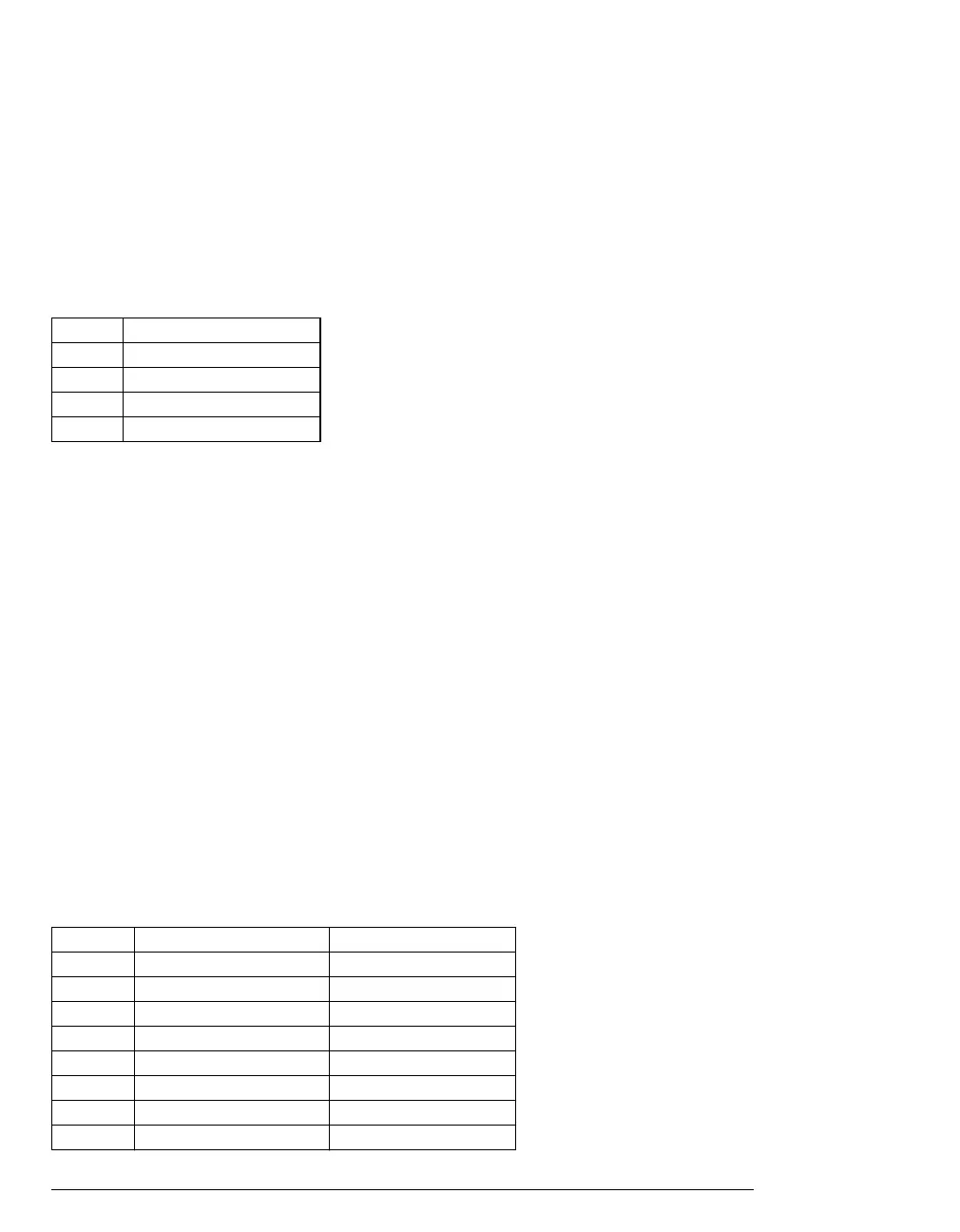

Table 14-9 Floating-Point Trap Type Values

ftt Floating-Point Trap Type Trap Signalled

0 None —

1

IEEE_754_exception fp_exception_ieee_754

2

unfinished_FPop fp_exception_other

3

unimplemented_FPop fp_exception_other

4

sequence_error fp_exception_other

5

hardware_error

—

6

invalid_fp_register

—

7 reserved —

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...