Sun Microelectronics

312

UltraSPARC User’s Manual

Undefined: The value of these bits are undefined on reads and must be masked

off by software.

IC_pdec: The two 4-bit pre-decode fields. The encodings are:

• Bits<3:2> = 00 CALL, BPA, FBA, FBPA or BA

• Bits<3:2> = 01 Not a CALL, JMPL, BPA, FBA, FBPA or BA

• Bits<3:2> = 10 Normal JMPL (do not use return stack)

• Bits<3:2> = 11 Return JMPL (use return stack)

• Bit<1> If clear, indicates a PC-relative CTI.

• Bit<0> If set, indicates a STORE.

Note: The predecode bits are not updated when instructions are loaded into the

cache with ASI_ICACHE_INSTR. They are only accurate for instructions loaded

by instruction cache miss processing.

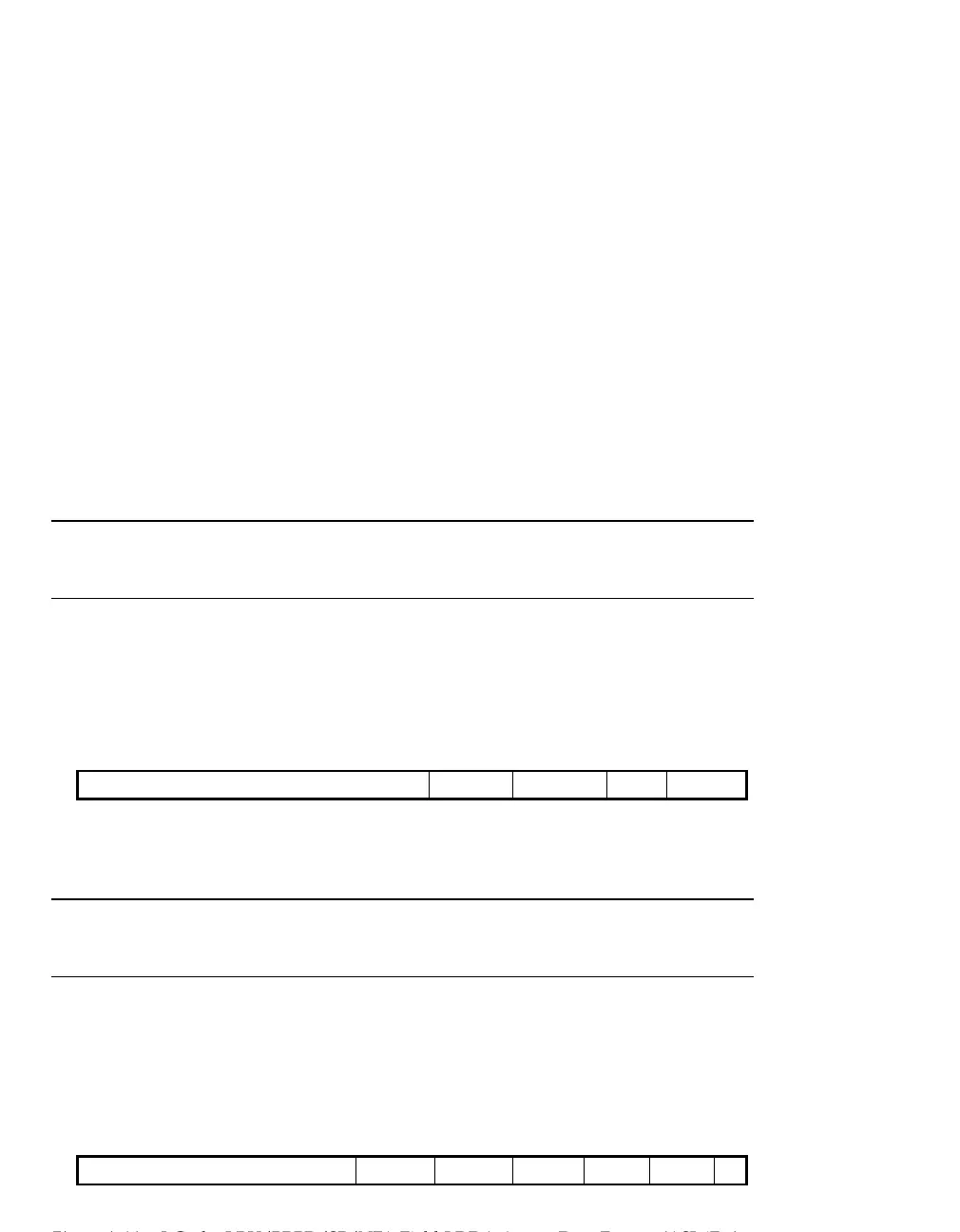

A.7.4 I-Cache LRU/BRPD/SP/NFA Fields

ASI 6F

16

, VA<63:14>=0, VA<13>=IC_set, VA<12:3>=IC_addr, VA<2:0>=0

Name: ASI_ICACHE_PRE_NEXT_FIELD

Figure A-13 I-Cache LRU/BRPD/SP/NFA Field Access Address Format (ASI 6F

16

)

Note: Stores to ASI_ICACHE_PRE_NEXT_FIELD are undefined unless the

instruction cache is disabled via the IC bit of the LSU control register (see

“LSU_Control_Register” on page 306).

IC_set: This 1-bit field selects a set (2-way associative).

IC_addr: this 8-bit index (addr <12:5>) selects an IC_Line.

IC_line: This 1-bit field selects two BRPD and one NFA fields for four 128-bit

aligned instructions.

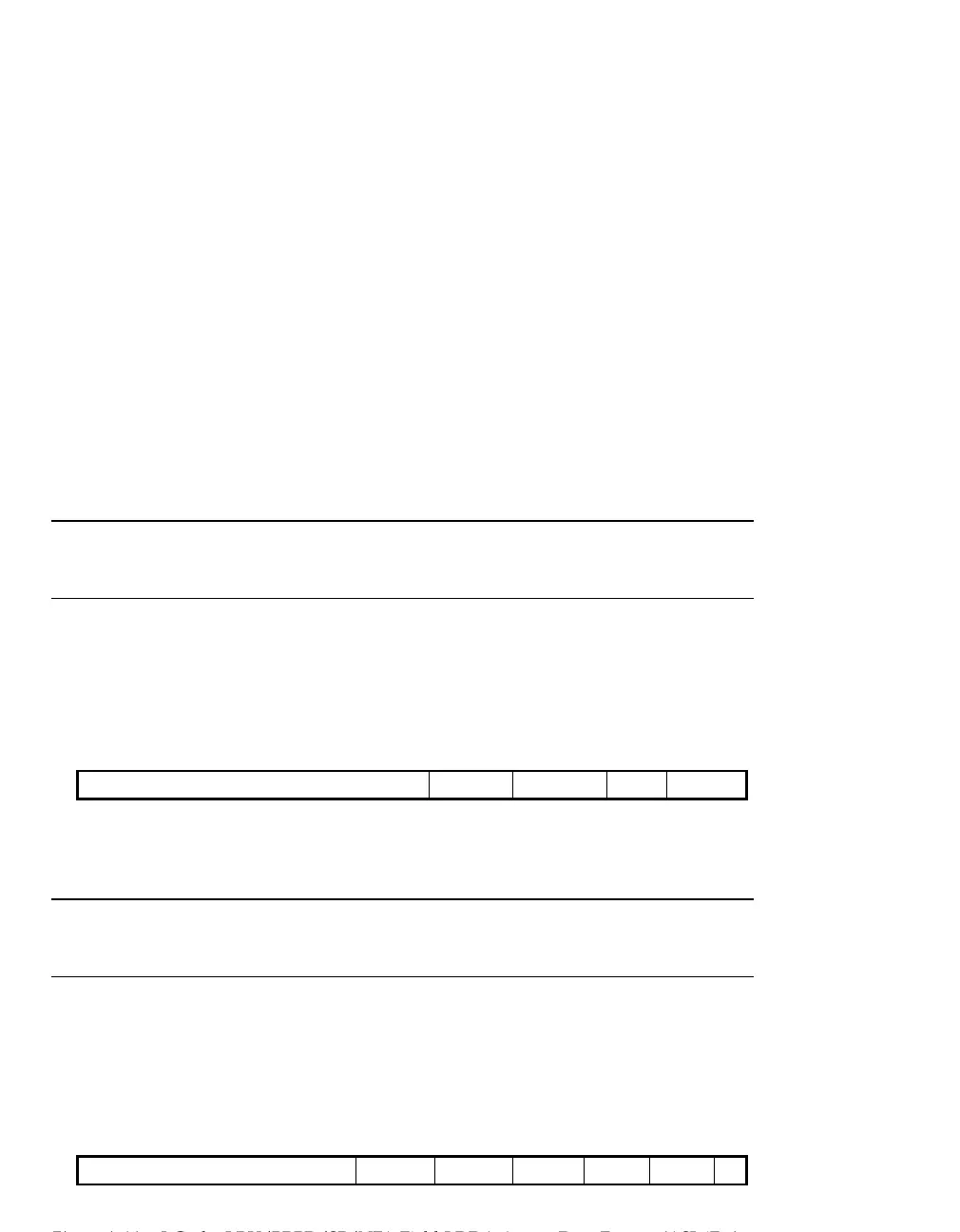

Figure A-14 I-Cache LRU/BRPD/SP/NFA Field LDDA Access Data Format (ASI 6F

16

)

63 340

—

—

IC_set

IC_addr

121314 5

IC_line

63 910 0

Undefined

IC_nfa

22

IC_sp

IC_lru

25 78

und.

122324

IC_brpd 0

IC_brpd 1

11

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...