Sun Microelectronics

37

5. Cache and Memory Interactions

• Some conditions, noted below, cause an otherwise supported PREFETCH to

be treated as a NOP and removed from the load buffer when it reaches the

front of the queue.

• No PREFETCH will cause a trap except:

• PREFETCH with fcn=5..15 causes an

illegal_instruction

trap, as defined in The

SPARC Architecture Manual, Version 9.

• Watchpoint, as defined in Section A.5, “Watchpoint Support,” on page 304.

• Any PREFETCHA that specifies an internal ASI in the following ranges is not

enqueued on the load buffer and is not executed:

• 40

16

..4F

16

, 50

16

..5F

16

, 60

16

..6F

16

, 76

16

, 77

16

• The following conditions cause a PREFETCH{A} to be treated as a NOP:

• PREFECTH with fcn=16..31, as defined in The SPARC Architecture Manual,

Version 9.

• A

data_access_MMU_miss

exception

• D-MMU disabled

• For PREFETCHA, any ASI other than the following 04

16

, 0C

16

, 10

16

, 11

16

,

18

16

, 19

16

, 80

16

..83

16

, 88

16

..8B

16

• Attempt to PREFETCH to a noncacheable page

• Alignment is not checked on PREFETCH{A}. The 5 least significant address

are ignored.

5.3.5.2 Implemented fcn Values

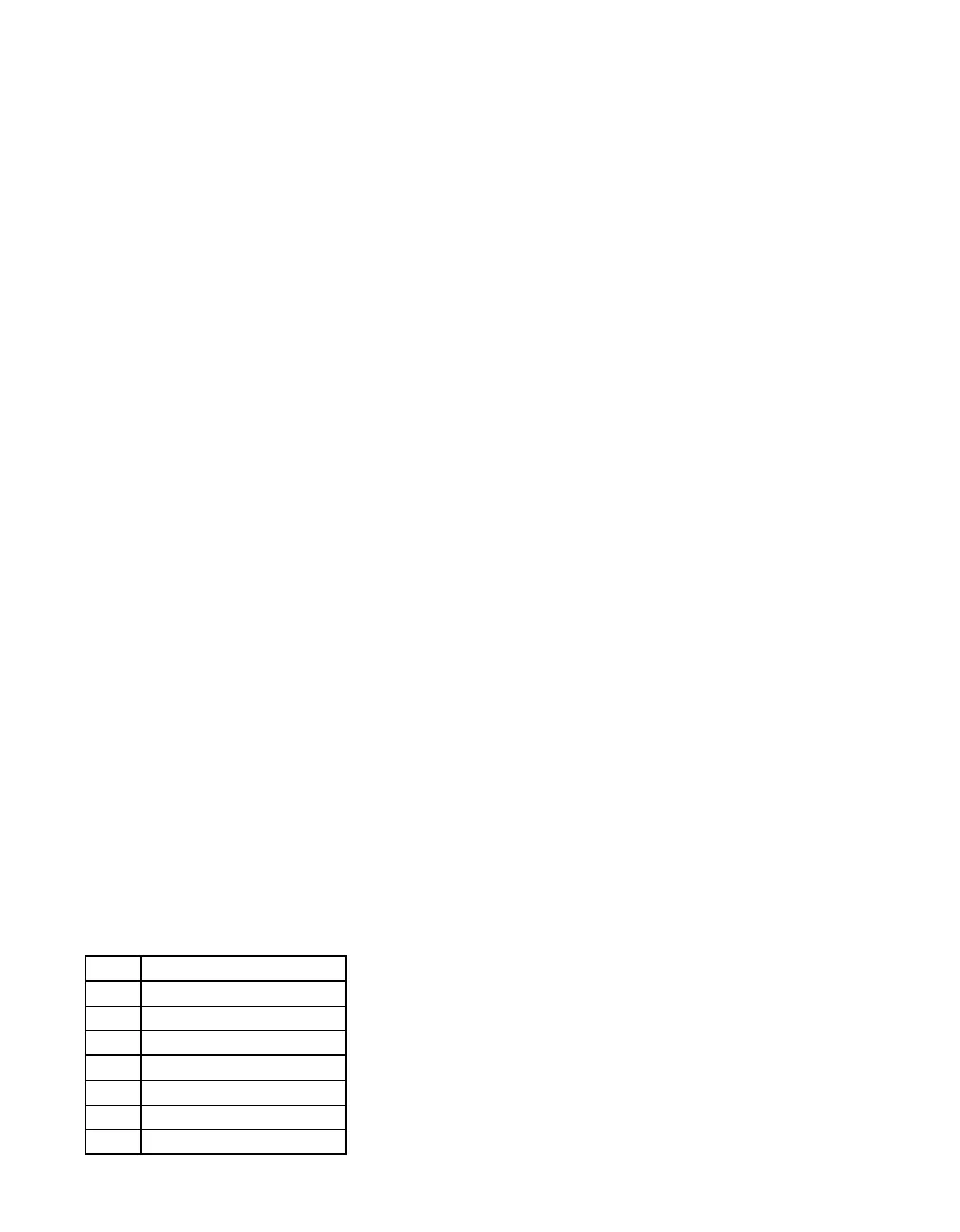

Table 5-3 lists the supported values for fcn and their meanings.

For more information, including an enumeration of the bus transaction the each

fcn value causes, see Section 14.4.5, “PREFETCH{A} (Impdep #103, 117),” on page

248.

Table 5-3 PREFETCH{A} Variants

fcn Prefetch Function

0 Prefetch for several reads

1 Prefetch for one read

2 Prefetch page

3 Prefetch for several writes

4 Prefetch for one write

5..15

illegal_instruction

trap

16..31 NOP

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...