Sun Microelectronics

36

UltraSPARC User’s Manual

Non-faulting loads are issued with ASI_PRIMARY_NO_FAULT{_LITTLE}, or

ASI_SECONDARY_NO_FAULT{_LITTLE}. A store with a NO_FAULT ASI causes

a

data_access_exception

trap (with SFSR.FT=8, Illegal RW).

When a non-faulting load encounters a TLB miss, the operating system should at-

tempt to translate the page. If the translation results in an error (for example, ad-

dress out of range), a 0 is returned and the load completes silently.

Typically, optimizers use non-faulting loads to move loads before conditional

control structures that guard their use. This technique potentially increases the

distance between a load of data and the first use of that data, in order to hide la-

tency; it allows for more flexibility in code scheduling. It also allows for im-

proved performance in certain algorithms by removing address checking from

the critical code path.

For example, when following a linked list, non-faulting loads allow the null

pointer to be accessed safely in a read-ahead fashion if the OS can ensure that the

page at virtual address 0

16

is accessed with no penalty. The NFO (non-fault access

only) bit in the MMU marks pages that are mapped for safe access by non-fault-

ing loads, but can still cause a trap by other, normal accesses. This allows pro-

grammers to trap on wild pointer references (many programmers count on an

exception being generated when accessing address 0

16

to debug code) while ben-

efitting from the acceleration of non-faulting access in debugged library routines.

5.3.5 PREFETCH Instructions

Table 5-2 shows which UltraSPARC models support the PREFETCH{A} instruc-

tions.

UltraSPARC models that do not support PREFETCH treat it as a NOP.

5.3.5.1 PREFETCH Behavior and Limitations

UltraSPARC processors that do support PREFETCH behave in the following

ways:

• All PREFETCH instructions are enqueued on the load buffer, except as noted

below.

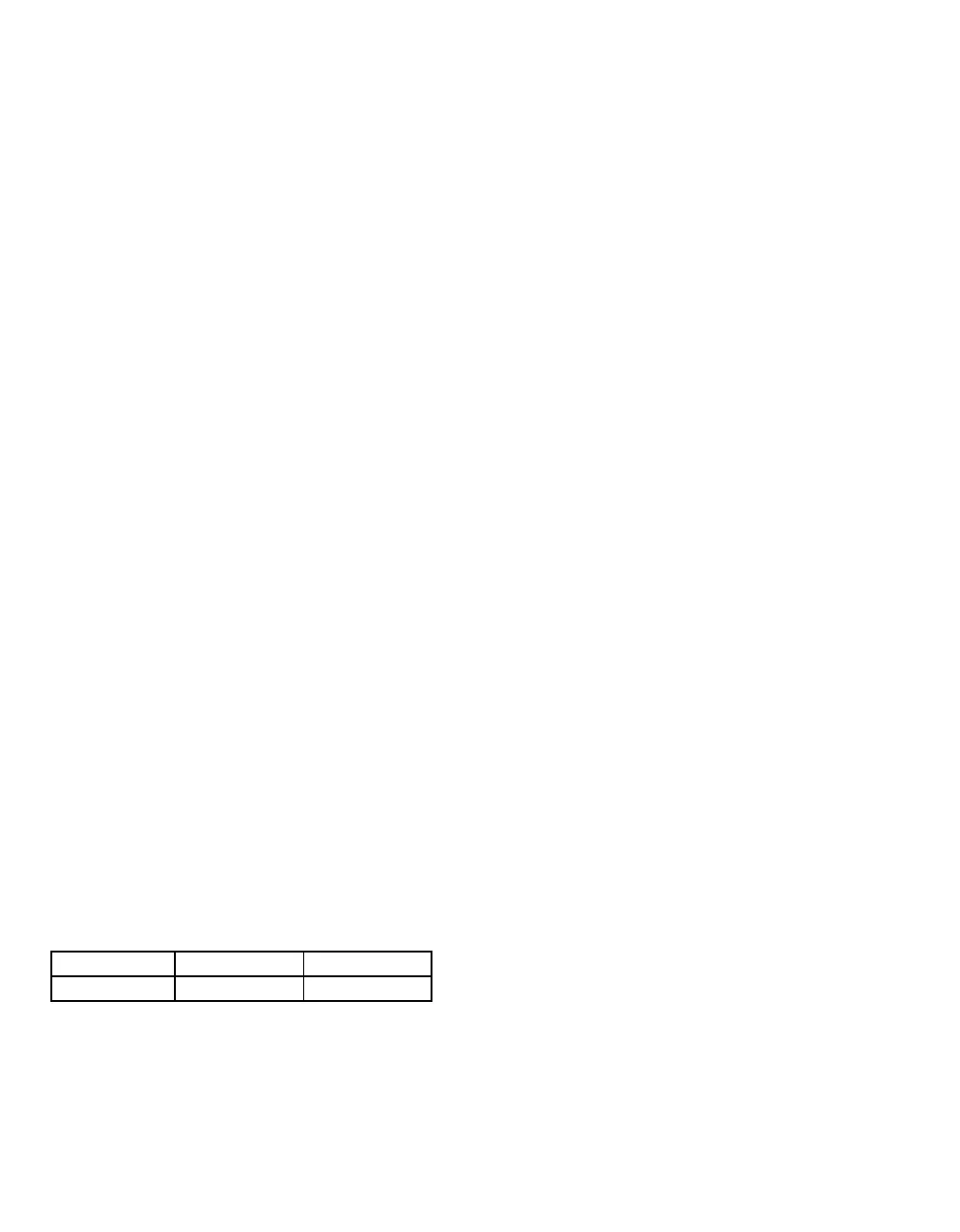

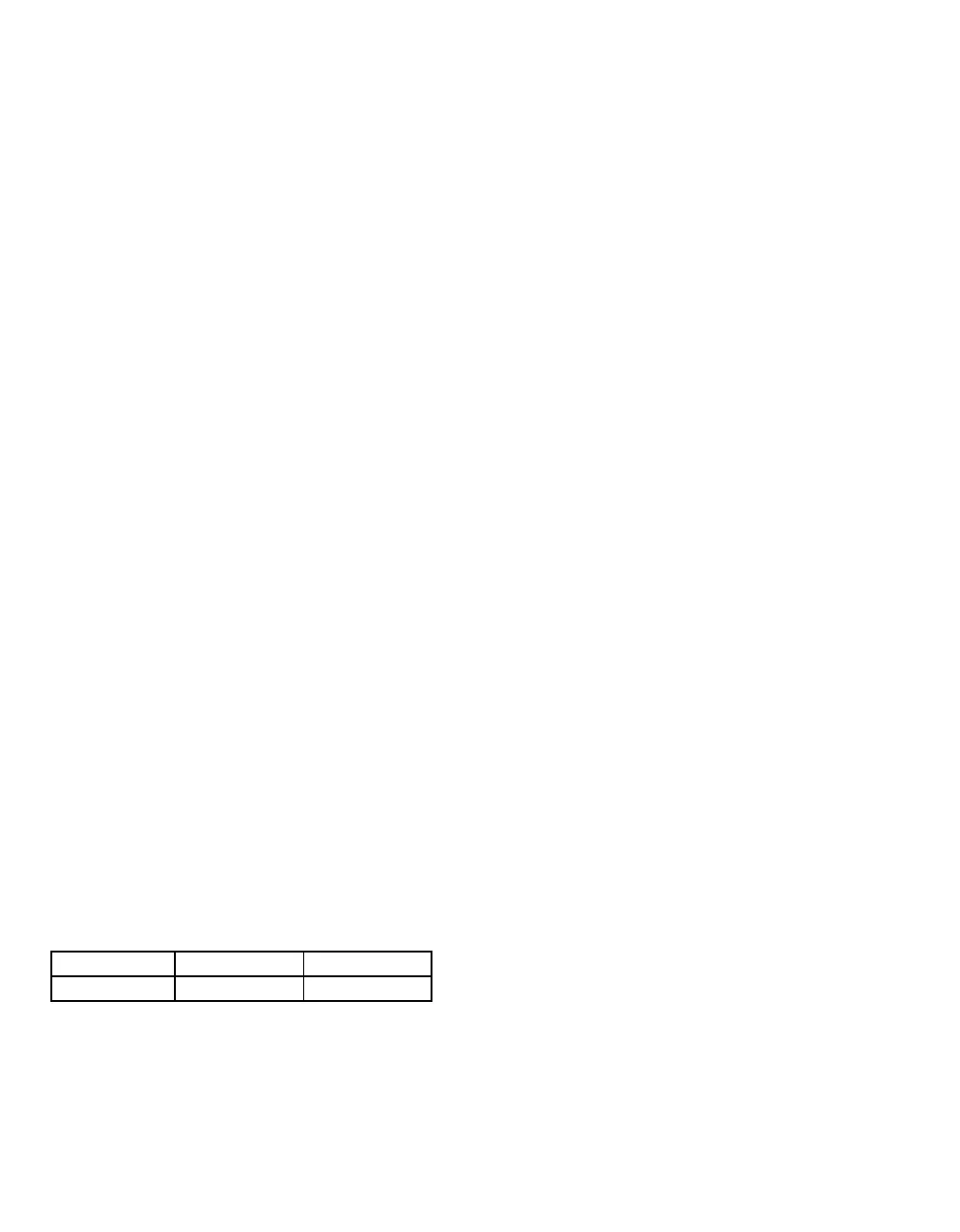

Table 5-2 PREFETCH{A} Instruction Support

UltraSPARC-I UltraSPARC-II

PREFETCH{A} ✓

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...