Sun Microelectronics

56

UltraSPARC User’s Manual

Warning – STXA to an MMU register requires either a MEMBAR #Sync, FLUSH,

DONE, or RETRY before the point that the effect must be visible to load / store /

atomic accesses. Either a FLUSH, DONE, or RETRY is needed before the point

that the effect must be visible to instruction accesses: MEMBAR #Sync is not

sufficient. In either case, one of these instructions must be executed before the

next non-internal store or load of any type and on or before the delay slot of a

DCTI of any type. This is necessary to avoid corrupting data.

If the low order three bits of the VA are non-zero in a LDXA/STXA to/from these

registers, a

mem_address_not_aligned

trap occurs. Writes to read-only, reads to

write-only, illegal ASI values, or illegal VA for a given ASI may cause a

data_access_exception

trap (FT=08

16

). (The hardware detects VA violations in only

an unspecified lower portion of the virtual address.)

Warning – UltraSPARC does not check for out-of-range virtual addresses during

an STXA to any internal register; it simply sign extends the virtual address based

on VA<43>. Software must guarantee that the VA is within range.

Writes to the TSB register, Tag Access register, and PA and VA Watchpoint Ad-

dress Registers are not checked for out-of-range VA. No matter what is written to

the register, VA<63:43> will always be identical on a read.

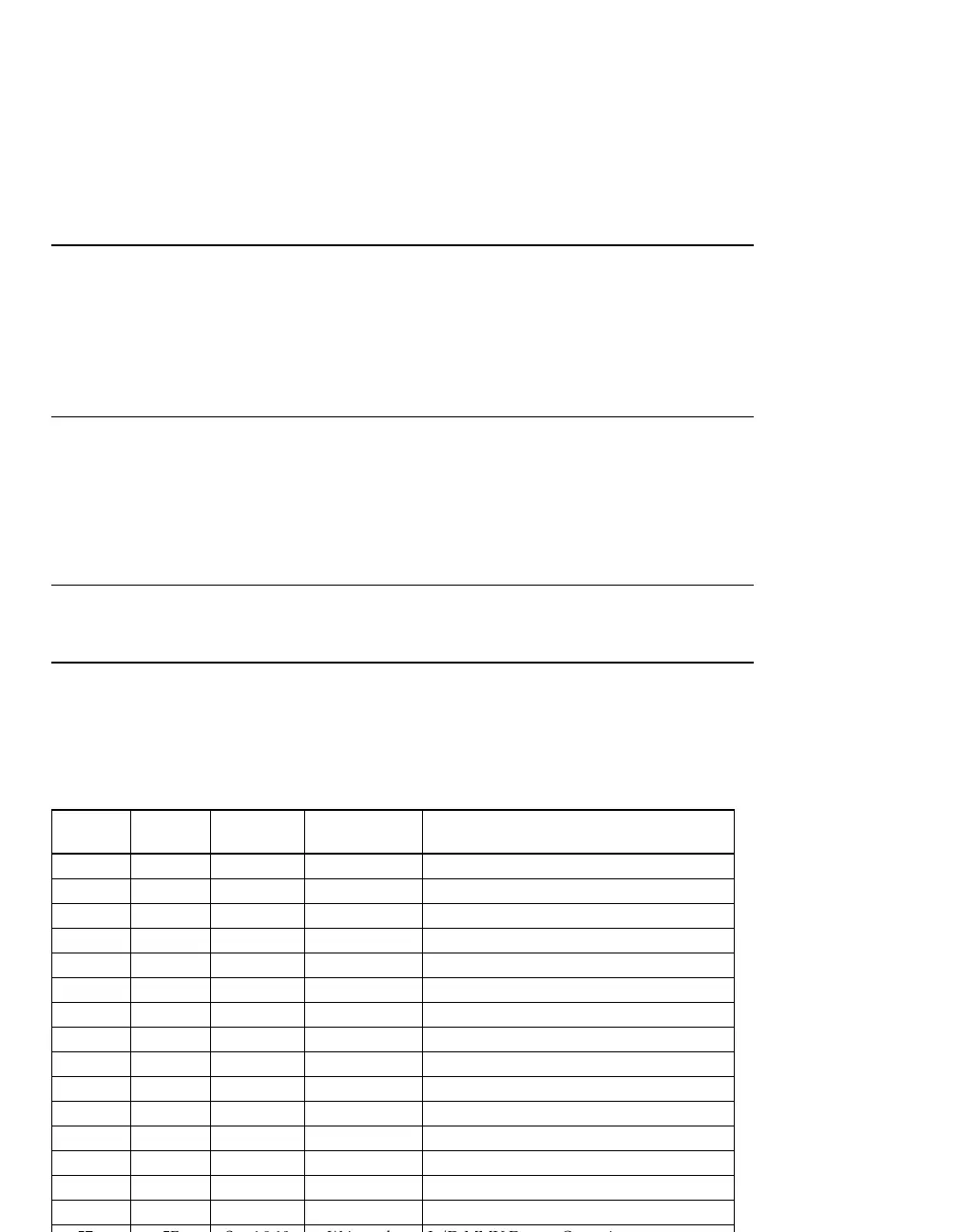

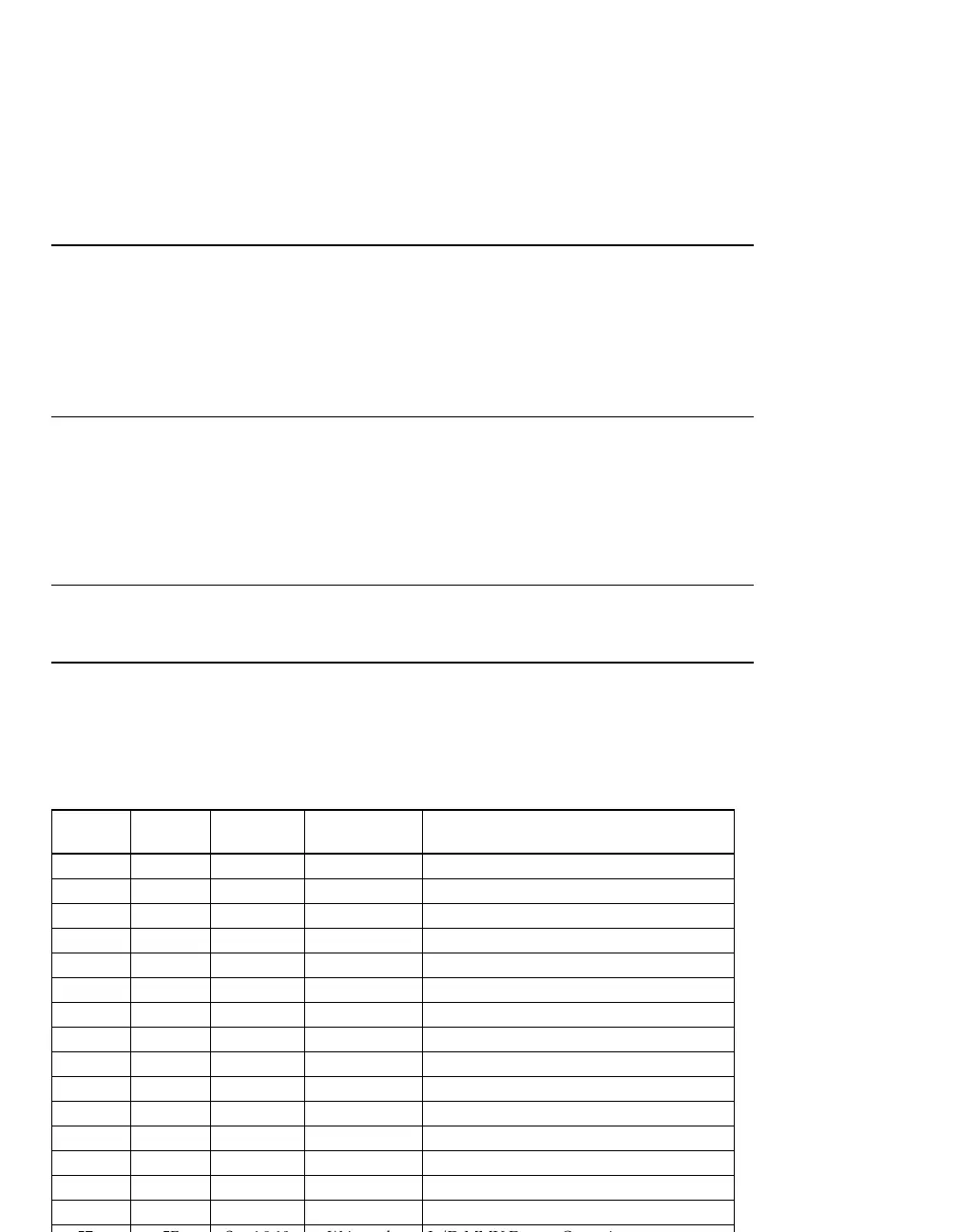

Table 6-10 UltraSPARC MMU Internal Registers and ASI Operations

I-MMU

ASI

D-MMU

ASI

VA<63:0> Access Register or Operation Name

50

16

58

16

0

16

Read-only I-/D-TSB Tag Target Registers

—58

16

8

16

Read/Write Primary Context Register

—58

16

10

16

Read/Write Secondary Context Register

50

16

58

16

18

16

Read/Write I-/D-Synchronous Fault Status Registers

—58

16

20

16

Read-only D Synchronous Fault Address Register

50

16

58

16

28

16

Read/Write I-/D-TSB Registers

50

16

58

16

30

16

Read/Write I-/D-TLB Tag Access Registers

—58

16

38

16

Read/Write Virtual Watchpoint Address

—58

16

40

16

Read/Write Physical Watchpoint Address

51

16

59

16

0

16

Read-only I-/D-TSB 8K Pointer Registers

52

16

5A

16

0

16

Read-only I-/D-TSB 64K Pointer Registers

—5B

16

0

16

Read-only D-TSB Direct Pointer Register

54

16

5C

16

0

16

Write-only I-/D-TLB Data In Registers

55

16

5D

16

0

16

..1F8

16

Read/Write I-/D-TLB Data Access Registers

56

16

5E

16

0

16

..1F8

16

Read-only I-/D-TLB Tag Read Register

57

16

5F See 6.9.10 Write-only I-/D-MMU Demap Operation

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...