Sun Microelectronics

81

7. UltraSPARC External Interfaces

data address is presented on the ECAD pins in the cycle after the request (cycle 4

for W0) and the data is sent in the following cycle (cycle 5). Systems running in

2–2 Mode incur no read-to-write bus turnaround penalty.

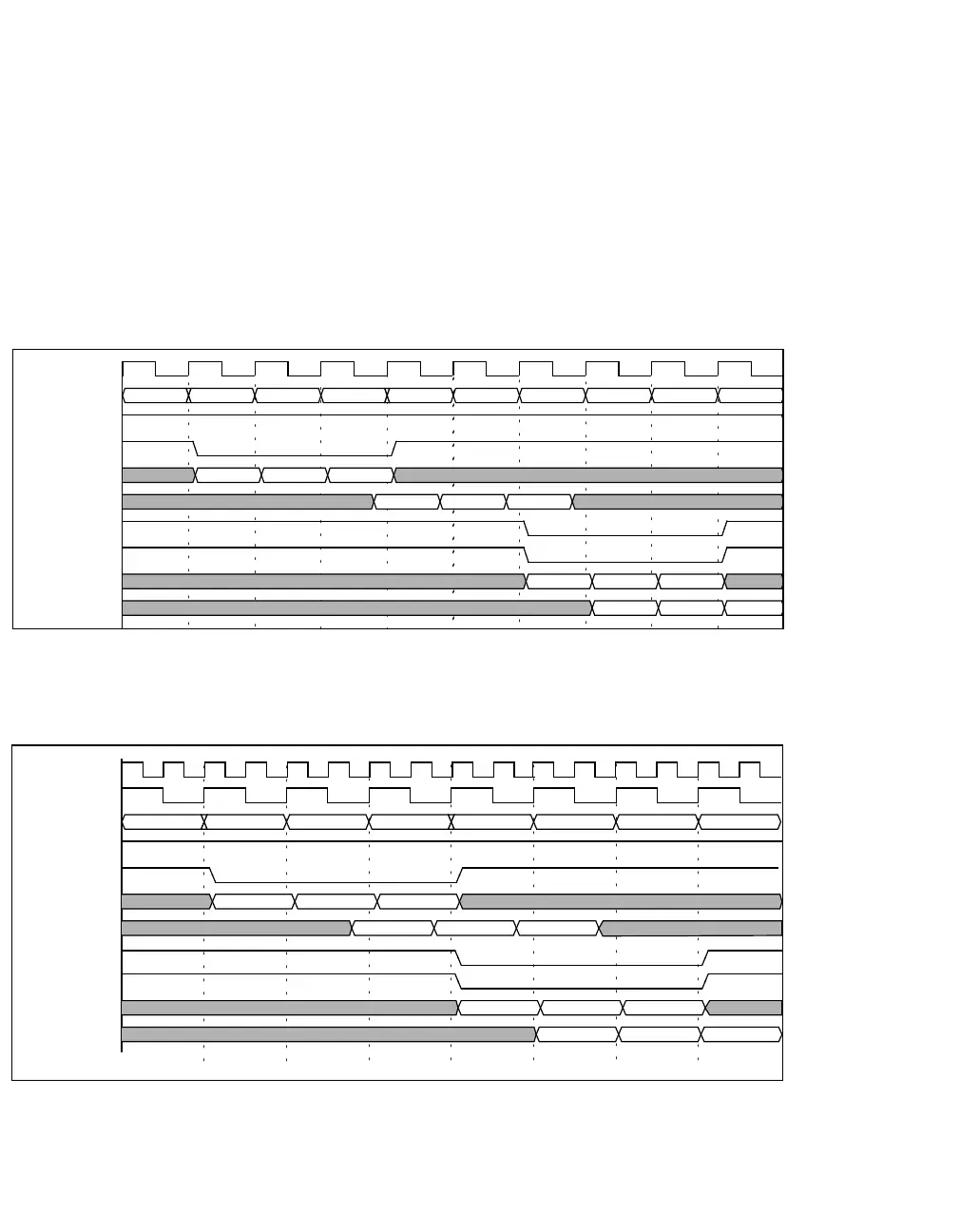

Figure 7-5 Timing for Coherent Write Hit to M State Line (1–1–1 Mode)

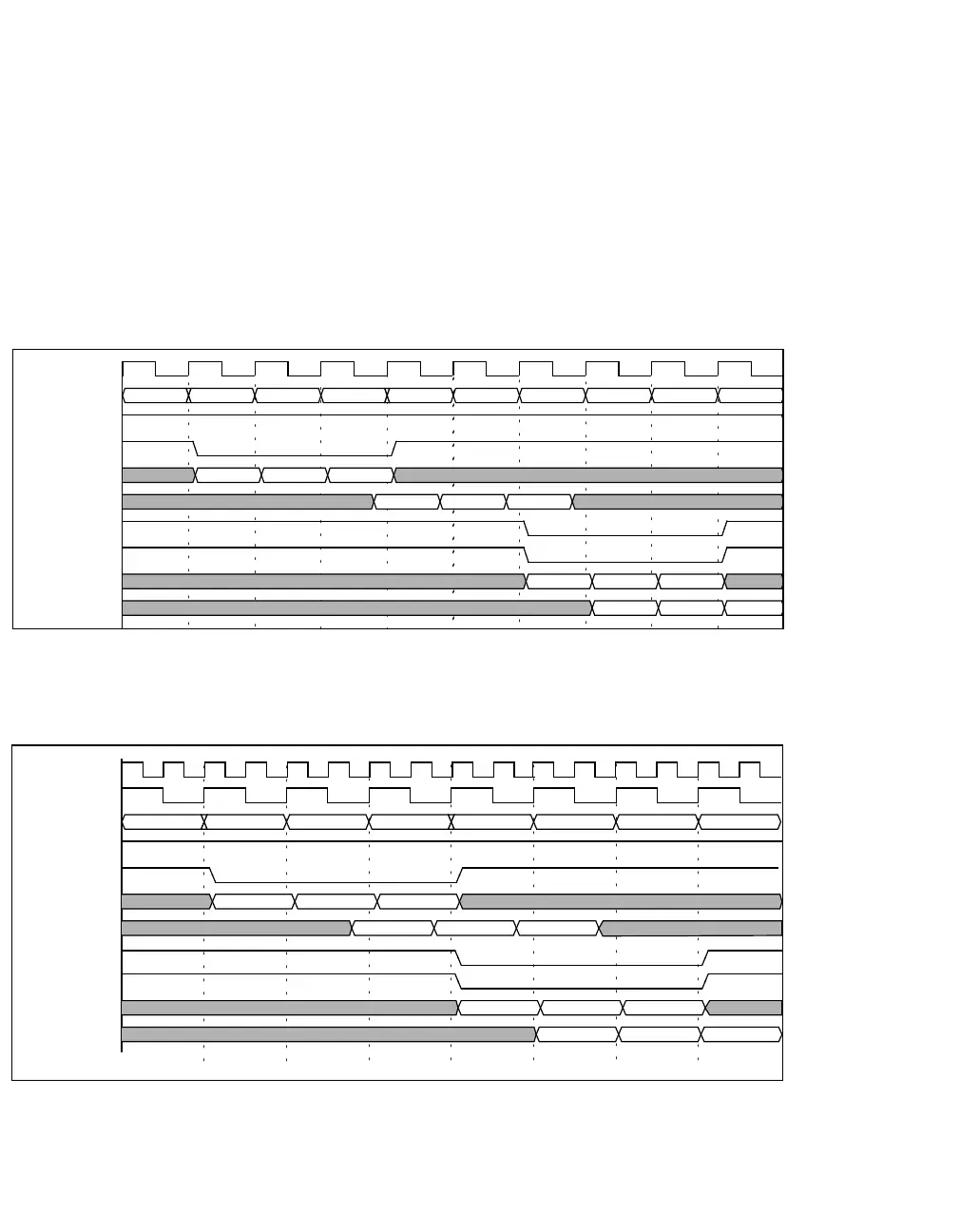

Figure 7-6 Timing for Coherent Write Hit to M State Line (2–2 Mode)

If the line is in Exclusive (E) state, the tag is updated to Modified (M) state at the

same time that the data is written, as shown in Figure 7-7 on page 82 (1–1–1

Mode).

CLK

CYCLE

0123456789

TSYN_WR_L

R0 R1 R2

TOE_L

R0 R1 R2

ECAT

A0_tag A1_tag A2_tag

TDATA

D0_tag D1_tag D2_tag

DSYN_WR_L

W0 W1 W2

DOE_L

W0 W1 W2

ECAD

A0_data A1_data A2_data

EDATA

D0_data D1_data D2_data

SRAM CLK

SRAM CYCLE

01234567

TSYN_WR_L

R0 R1 R2

TOE_L

R0 R1 R2

ECAT

A0_tag A1_tag A2_tag

TDATA

D0_tag D1_tag D2_tag

DSYN_WR_L

DOE_L

W0 W1 W2

ECAD

A0_data A1_data A2_data

EDATA

D0_data D1_data D2_data

CPU CLK

W0 W1 W2

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...